分类号: \_\_\_\_\_TN4\_\_\_\_

单位代码: 10335

学 号: 21931072

## 浙江大学

## 硕士学位论文

| 中文论文题目: | 低功耗 2-0 MASH ADC 的     |

|---------|------------------------|

|         | 研究与设计                  |

| 英文论文题目: | Research and Design of |

|         | Low Power 2-0 MASH ADC |

| 申请人姓名:     | 胡耀鹏        |

|------------|------------|

| 指导教师:      | 赵梦恋 副教授    |

| 合作导师:      | 谭志超 研究员    |

| 专业名称:      | 电子科学与技术    |

| 研究方向:      | 混合信号 IC 设计 |

| —<br>所在学院: | 信息与由子丁程学院  |

论文提交日期 2022 年 1 月

## 低功耗 2-0 MASH ADC 的研究与设计

论文作者签名: 胡椒鹃 指导教师签名: 女女女

| 论文评阅人1:    | 匿名                |

|------------|-------------------|

| 评阅人 2:     | 匿名                |

| 评阅人3:      | 匿名                |

| 评阅人 4:     |                   |

| 评阅人 5:     |                   |

| 1          |                   |

| 答辩委员会主席: _ | 赵民建 教授 浙江大学       |

| 委员1:_      | 郑史烈 教授 浙江大学       |

| 委员 2: _    | 余官定 教授 浙江大学       |

| 委员 3: _    | 林宏焘 研究员 浙江大学      |

| 委员 4: _    | 何先华 高级工程师         |

|            | 诺基亚通信投资 (中国) 有限公司 |

| 委员 5: _    |                   |

答辩日期: 2022年3月/0日

## 独创性声明

本人声明所呈交的学位论文是本人在导师指导下进行的研究工作及取得的 研究成果。据我所知,除了文中特别加以标注和致谢的地方外,论文中不包含其 他人已经发表或撰写过的研究成果,也不包含为获得 浙江大学 或其他教育机 构的学位或证书而使用过的材料。与我一同工作的同志对本研究所做的任何贡献 均已在论文中作了明确的说明并表示谢意。

学位论文作者签名: 耐福的 签字日期: 2012年 3月14日

## 学位论文版权使用授权书

本学位论文作者完全了解 浙江大学 有关保留、使用学位论文的规定, 有权保留并向国家有关部门或机构送交论文的复印件和磁盘,允许论文被查阅和 借阅。本人授权 浙江大学 可以将学位论文的全部或部分内容编入有关数据库 进行检索,可以采用影印、缩印或扫描等复制手段保存、汇编学位论文。

(保密的学位论文在解密后适用本授权书)

学位论文作者签名: 胡耀艳

导师签名: 艺技

签字日期: 2022年 3月14日

签字日期: 202 年 3 月16日

## 致谢

时间总是过的飞快,研究生的两年半生活也快要结束了。在这段令人难忘的时光中,有令人难过的困难,当然,也有许多快乐和喜悦。在此,我想向陪我一同共度难关,一同分享喜悦的人们致以诚挚的感谢。

首先,我想在此感谢吴晓波老师、赵梦恋老师和谭志超老师对我的耐心指导。 我并不是一个基础很好的学生,还经常会因为粗心大意而犯错。有幸能够提前进入实验室接触研究生生活,所以也能够用更多的时间去学习和积累来弥补自己的不足。然而,投入更多的时间虽然能够把一堆事情做不差,却难以把一件事情做好。在这个过程中,三位老师的指导真的给了我太大的帮助,不论是研究方向上的建议、研究过程中对于细碎问题的解答,还有最后对论文的详细修改意见,这些都让我学到了很多。最终,让我在毕业之前能够有能力做好一些事情,也取得了一些成果。

其次,我还想要感谢实验室这个大家庭中的同学们。感谢白雪彤师姐和杨朝师兄、刘胜师兄在我刚进入实验室时对我的关心指导以及学习上的建议。感谢杨小林、姚焱遐、赵依博、张丹妮、邬明州等师兄师姐在我遇到困难时给予的帮助。感谢同期好友李梦雨、杨宇、张泽琪的一同努力。感谢孟龄欣、寇毓臻、季怀坤、陆召南、陈君胜、郝茜蕤等师弟师妹们的陪伴。

感谢张卓、张铖洪、王泽元三位室友的朝夕相处,对我的学习和各种专业知识上的帮助。感谢蒋晨威、解志千、杨轶伦三位好友的鼓励与支持。希望你们能够在以后的学习以及工作中一切顺利。

最后,我想要感谢我亲爱的父母和岳灵婧同学。十分感谢你们不论何时都能理解与支持我,是你们的关心、鼓励与信任才能够让我走到今天。我并不优秀,也不是很有干劲,有着懒惰等各种各样的缺点。如果没有你们的一路相伴,面对这大大小小的困难我可能早就会选择放弃。希望你们能够在以后的生活中健康顺心,也希望自己能够成长为你们可以相信与依靠的人,希望今后能够和你们一起走下去。

I

## 摘要

作为当今社会发展热点,物联网设备正在逐渐融入人们生产生活各个方面,使得智能传感器越来越普及。作为其中的核心器件,ADC的需求量在逐渐上升。考虑到其严苛的电源环境,ADC的低功耗设计显得尤为重要;同时,为了满足分辨率需求以及适应复杂的应用场景,ADC的信噪比以及PVT稳定性要求也越来越高。

ΔΣ ADC 适用于高精度、低功耗场合,通过过采样与噪声整形技术,可以有效降低带内噪声。更高的阶数具有更好的噪声整形效果,但也具有更容易饱和的缺点。MASH ADC 可以在相对低阶的环路稳定要求基础上,实现更高的信噪比。本文结合传感器应用领域低功耗、高动态范围的设计要求,研究和设计了低功耗2-0 MASH ADC。

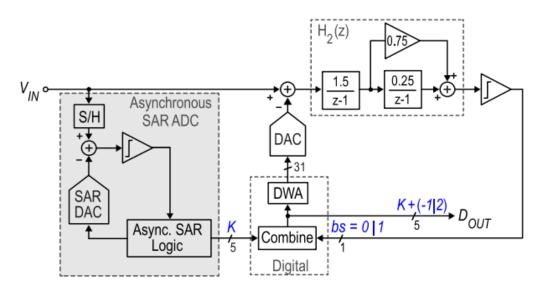

论文设计的 2-0 MASH ADC 采用数字前馈型结构。第一级 ADC 采用 SAR ADC 作为前馈支路量化器,其输出结果与比较器输出结果相结合,作为第一级 ADC 的量化结果,这种数字前馈结构实质是 Zoom ADC。此时,反馈 DAC 变为 bit。这有利于减小积分器信号摆幅并减小功耗。在电路层面,本文创新地提出了一种动态体偏置辅助的相关电平漂移技术,在仅采用一个供电电容条件下,将单级浮动反相放大器的直流增益提高到 66dB 以上。

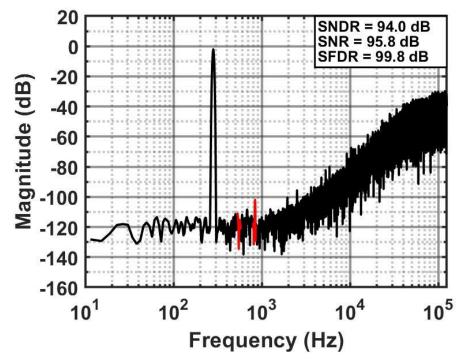

本文提出的 2-0 MASH ADC 采用 TSMC 55nm CMOS 工艺,芯片核心面积为  $0.136\text{mm}^2$ ,信号带宽为 1kHz。测试结果表明芯片在 1.2V 电源电压下,功耗为  $2.87\mu\text{W}$ ,在 278.5Hz、-1.9dBFS输入时,测得的 SNDR、SNR 和 SFDR 分别为 94.0dB、95.8dB 和 99.8dB,实现了高达 179.4dB 的  $\text{FoM}_{\text{SNDR}}$  和 182.3dB 的  $\text{FoM}_{\text{DR}}$ 。同时,在电源电压变化的情况下,可以保证相对稳定的工作。

关键词: MASH ADC, 高精度, 低功耗, 浮动反相放大器, 相关电平偏移

浙江大学硕士学位论文 Abstract

#### **Abstract**

As a hot spot of social development, Internet of Things (IoT) devices are gradually integrating into all aspects of people's production and life, making intelligent sensors more and more popular. As the core device, the demand for ADC is gradually increasing. Considering the harsh power environment, low-power ADC design is particularly important. At the same time, in order to meet the resolution requirements and adapt to complex application scenarios, the signal to noise ratio and PVT stability of ADC are meeting more and more strict requirements.

$\Delta\Sigma$  ADC is suitable for high-precision and low-power applications. By oversampling and noise shaping, it can effectively reduce in-band noise. Higher order has sharp noise transfer function, but it also has the disadvantage that the system is easier to saturate. MASH ADC can achieve higher signal-to-noise ratio (SNR) with relatively low-order loop stability requirements. Considering low power consumption and high precision design in sensor application field, a low power 2-0 MASH ADC is proposed in this thesis.

The 2-0 MASH ADC proposed in this thesis adopts digital feedforward structure. The first stage ADC uses SAR ADC as the feedforward branch quantizer and its output is combined with the comparator output as the quantization result of the first stage ADC, where digital feedforward structure is essentially the Zoom ADC. Meanwhile, the feedback DAC becomes multi bit, which could help to reduce the integrator signal swing and reduce power consumption. At the circuit level, a dynamic-body-biasing assisted correlated level shifting (CLS) technique is proposed to boost the DC gain of a single-stage floating inverter amplifier (FIA) with only one reservoir capacitor to above 66 dB.

The prototype 2-0 MASH ADC is fabricated in TSMC 55nm CMOS process and its core area is  $0.136 \text{mm}^2$ . The signal bandwidth is 1kHz. The experiment measurement results show that the power consumption is  $2.87~\mu\text{W}$  at the power supply voltage 1.2V. The measured SNDR, SNR and SFDR are 94.0 dB, 95.8 dB and 99.8 dB with -1.9 dBFS

浙江大学硕士学位论文 Abstract

input at 278.5Hz respectively. The prototype ADC achieves an  $FoM_{SNDR}$  of 179.4dB and an  $FoM_{DR}$  of 182.3dB. When the power supply voltage changes, it can still maintain relatively stable operation.

**Keywords**: MASH ADC, high precision, low power, floating inverter amplifier, correlated level shifting

浙江大学硕士学位论文 缩略词表

## 缩略词表

**VCO**

亚德诺半导体 ADI Analog Devices Inc. **CIFF** Cascade of Integrators with feed forward 前馈型级联积分器 CLS Correlated Level Shift 相关电平偏移 共模反馈 **CMFB** Common Mode Feedback CTContiuns Time 连续时间 DA **Dynamic Amplifier** 动态放大器 设计规则验证 DRC Design Rule Check 离散时间 DT Discrete Time 数据加权平均法 **DWA** Data-weighted Average 有效位数 **ENOB** Effective Number of Bits FIA 浮动反相器运算放大器 Floating Inverter Amplifier 品质因数 FoM Figure of Merit **FSR** Full Scale Range 满量程 谐波失真 HD Harmonic Distortion 高阈值电压 MOS 管 **HVT MOS** High V<sub>th</sub> MOSFET 低压差线性稳压器 LDO Low Dropout linear regulator MASH 多级噪声整形 Multi-stage Noise Shaping MC Montre Carlo 蒙特卡洛 噪声整形 NS Noise Shaping 噪声传递函数 NTF Noise Transfer Function 过采样率 **OSR** Oversampling Rate 可编程增益放大器 **PGA** Programmable Gain Amplifier SAR 逐次逼近型 Successive Approximation **SEFIA** 摆幅增强型浮动反相放大器 Swing Enhanced FIA 无杂散动态范围 **SFDR** Spurious Free Dynamic Range 信号-噪声失真比 SINAD/SNDR Signal-to-Noise-and-Distortion Ratio 稳定型 MASH **SMASH** Sturdy MASH **SNC** 采样 kT/C 噪声消除技术 Sampling kT/C Noise Cancellation 信号-噪声比 **SNR** Signal-to-Noise Ratio 信号传递函数 STF Signal Transfer Function 德州仪器 ΤI **Texas Instruments**

Voltage Controlled Oscillator

压控振荡器

## 目录

| 致谢       |        | I                  |

|----------|--------|--------------------|

| 摘要       |        | II                 |

| Abstract |        | III                |

| 缩略词表     | 隻      | V                  |

| 目录       |        | VI                 |

| 插图和图     | 付表目录   | ĮXIX               |

| 1 绪论     |        | 1                  |

| 1.1      | 研究背    | 景及意义1              |

| 1.2      | 国内外    | 研究现状1              |

|          | 1.2.1  | 学术界研究现状2           |

|          | 1.2.2  | 产业界调研4             |

| 1.3      | 论文内    | 容及结构安排6            |

| 2 MA     | SH ADO | C 技术基础8            |

| 2.1      | ADC ‡  | 支术指标8              |

|          | 2.1.1  | 基本特性参数8            |

|          | 2.1.2  | 静态性能参数9            |

|          | 2.1.3  | 动态性能参数9            |

|          | 2.1.4  | 数字和开关性能指标10        |

| 2.2      | ΔΣ ΑD  | C 基本理论10           |

|          | 2.2.1  | 量化噪声11             |

|          | 2.2.2  | 过采样                |

|          | 2.2.3  | 噪声整形               |

|          | 2.2.4  | 二阶 ΔΣ ADC          |

| 2.3      | MASH   | ADC 的工作原理16        |

|          | 2.3.1  | 多级 ADC 拓扑结构与信号分析16 |

|          | 2.3.2  | MASH ADC 信号分析      |

|          | 2.3.3  | SMASH ADC          |

|   |     | 2.3.4 | Zoom ADC             | .19 |

|---|-----|-------|----------------------|-----|

|   | 2.4 | 积分器   |                      | .20 |

|   |     | 2.4.1 | 积分器传递函数              | .20 |

|   |     | 2.4.2 | 开关电容电路噪声分析           | .22 |

|   | 2.5 | 动态元   | 件匹配                  | .23 |

|   |     | 2.5.1 | 随机选择法                | .24 |

|   |     | 2.5.2 | 数据加权平均法              | .24 |

|   | 2.6 | 本章小   | 结                    | .26 |

| 3 | 系统  | 架构和   | 理论分析                 | .27 |

|   | 3.1 | 系统设   | 计指标                  | .27 |

|   | 3.2 | 系统架   | 构设计                  | .28 |

|   |     | 3.2.1 | 系统参数确定               | .29 |

|   |     | 3.2.2 | 系统电路架构               | .33 |

|   | 3.3 | 系统关   | 键技术                  | .33 |

|   |     | 3.3.1 | CHOPPER 开关           | .33 |

|   |     | 3.3.2 | CDAC 复用              | .34 |

|   |     | 3.3.3 | SAR 量化器及复用           | .35 |

|   | 3.4 | 本章小   | 结                    | .36 |

| 4 | 系统  | 模块电   | 路设计                  | .37 |

|   | 4.1 | 放大器   | 设计                   | .37 |

|   |     | 4.1.1 | 基于反相器的运算放大器设计        | .37 |

|   |     | 4.1.2 | 电平偏移增益提高技术           | .39 |

|   |     | 4.1.3 | 结合电平偏移增益提高技术的浮动反相放大器 | .43 |

|   |     | 4.1.4 | 动态体偏置                | .45 |

|   | 4.2 | SAR 量 | :化器                  | .47 |

|   |     | 4.2.1 | 动态比较器                | .47 |

|   |     | 4.2.2 | SAR 逻辑               | .48 |

|   |     | 4.2.3 | 量化器仿真结果              | .49 |

|   | 43  | 升压开   | <b>≠</b>             | 50  |

|    | 4.4      | DEM 4 | 莫块            | 51 |

|----|----------|-------|---------------|----|

|    | 4.5 时钟模块 |       |               |    |

|    | 4.6      | 本章小   | 结             | 53 |

| 5  | 版图       | ]设计与  | 仿真及测试结果       | 54 |

|    | 5.1      | 系统功   | 能验证           | 54 |

|    |          | 5.1.1 | 量化噪声仿真结果      | 54 |

|    |          | 5.1.2 | 系统整体仿真        | 55 |

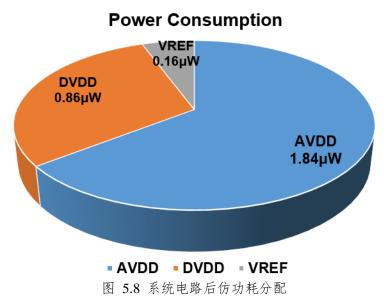

|    |          | 5.1.3 | 功耗分配          | 57 |

|    | 5.2      | 版图设   | 计和后仿验证        | 58 |

|    |          | 5.2.1 | 版图设计          | 58 |

|    |          | 5.2.2 | 系统后仿指标验证      | 60 |

|    | 5.3      | 芯片测   | 试             | 62 |

|    |          | 5.3.1 | 测试 PCB        | 62 |

|    |          | 5.3.2 | 系统测试结果        | 64 |

|    |          | 5.3.3 | 动态范围测试        | 65 |

|    |          | 5.3.4 | 电源电压变化影响      | 66 |

|    | 5.4      | 本章小   | 结             | 66 |

| 6  | 总结       | 与展望   |               | 68 |

| 参考 | <b></b>  | 犬     |               | 70 |

| 作者 | 首简后      | 万及在攻  | 区读学位期间取得的科研成果 | 76 |

|    |          | 作者简   | 5历            | 76 |

|    |          | 发表的   | 7主要论文和专利      | 76 |

## 插图和附表目录

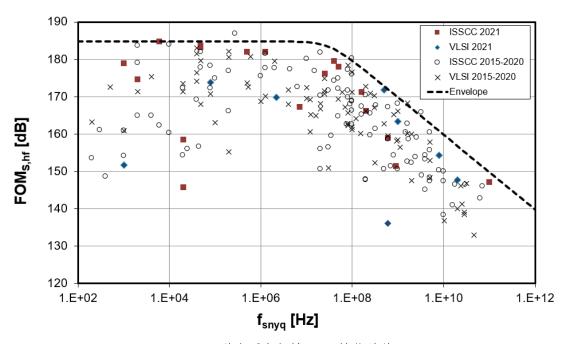

| 图 | 1.1 学术研究领域 FoM 性能总结                                                           | 2   |

|---|-------------------------------------------------------------------------------|-----|

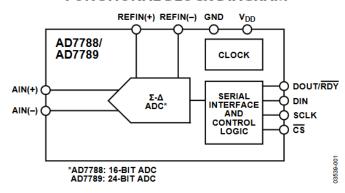

| 图 | 1.2 AD7788/7789 功能框图                                                          | 5   |

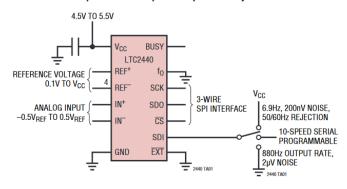

| 图 | 1.3 LTC2440 典型应用                                                              | 5   |

| 图 | 1.4 TLA202x 典型应用                                                              | 6   |

| 图 | 2.1 量化器输入-输出曲线                                                                | .11 |

| 图 | 2.2 过采样工作原理                                                                   | .12 |

| 图 | 2.3 一阶 ΔΣ ADC 结构框图                                                            | .13 |

| 图 | 2.4 一阶 ΔΣ ADC 频域噪声整形 <sup>[20]</sup>                                          | .13 |

| 图 | 2.5 二阶 ΔΣ ADC 结构框图                                                            | .14 |

| 图 | 2.6 Silva–Steensgaard $\stackrel{\frown}{=}$ $\stackrel{\frown}{\sim}$ ΔΣ ADC | .15 |

| 图 | 2.7 Silva-Steensgaard 二阶 ΔΣ ADC 输出频谱(2 <sup>16</sup> 点)                       | .15 |

| 图 | 2.8 Lesli-Singh 结构框图                                                          | .16 |

| 图 | 2.9 MASH ADC 结构框图                                                             | .18 |

| 图 | 2.10 SMASH ADC 结构框图                                                           | .19 |

| 图 | 2.11 Zoom ADC 结构框图                                                            | .20 |

| 图 | 2.12 开关电容积分器                                                                  | .20 |

| 图 | 2.13 CT 型积分器                                                                  | .21 |

| 图 | 2.14 导通时 MOS 开关的噪声模型和开关电容电路噪声模型                                               | .22 |

| 图 | 2.15 数字加权平均法循环模型                                                              | .25 |

| 图 | 3.1 ADC 结构框图                                                                  | .29 |

| 图 | 3.2 扩界系数与参考电压关系                                                               | .30 |

| 图 | 3.3 SQNR 与运放直流增益关系仿真图                                                         | .30 |

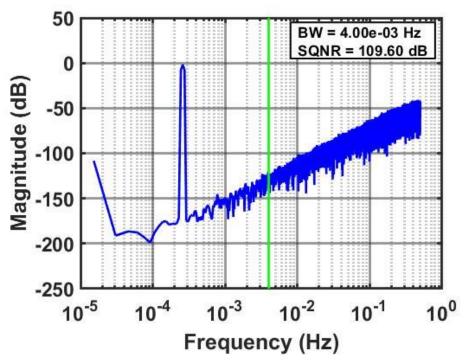

| 图 | 3.4 系统典型 FFT 输出频谱(2 <sup>16</sup> 点)                                          | .31 |

| 图 | 3.5 前馈系数扰动与 SQNR 分布直方图                                                        | .32 |

| 图 | 3.6 2-0 MASH ADC 电路结构图                                                        | .33 |

| 图 | 3.7 斩波开关与 1/f 噪声频谱分析                                                          | .34 |

| 图 | 38 采样/反馈电容独立型反馈结构                                                             | 35  |

| 图  | 3.9 采样/反馈电容复用型反馈结构                             | .35 |

|----|------------------------------------------------|-----|

| 图  | 3.10 SAR ADC 电路结构与时序图                          | .36 |

| 图  | 4.1 采用反相器运放的开关电容电路图                            | .38 |

| 图  | 4.2 反相器运放直流增益/增益带宽积与供电电压关系图                    | .38 |

| 图  | 4.3 反相器运放的开关电容电路共模反馈电路图                        | .39 |

| 图  | 4.4 CLS 电路工作原理与关键波形                            | .40 |

| 图  | 4.5 采用 CLS 技术的反相器运放电路与时序图                      | .41 |

| 图  | 4.6 采用 CLS 技术的反相器运放直流增益与输入幅值关系图                | .41 |

| 图  | 4.7 浮动反相放大器 FIA 电路图                            | .42 |

| 图  | 4.8 浮动反相放大器共模电流分析模型                            | .43 |

| 图  | 4.9 浮动反相放大器输出共模电压/增益与输入共模电压关系仿真结果              | .43 |

| 图  | 4.10 结合 FIA 与 CLS 技术的电路工作时序                    | .45 |

| 图  | 4.11 动态体偏置辅助的 FIA+CLS 电路工作时序                   | .46 |

| 图  | 4.12 动态体偏置辅助的 FIA+CLS 电路关键波形仿真图                | .46 |

| 图  | 4.13 系统第一级积分器输出信号分布直方图及运放直流增益与输出信号             | 分幅  |

| 值: | 关系                                             | .47 |

| 图  | 4.14 动态比较器电路图                                  | .48 |

| 图  | 4.15 SAR ADC 控制逻辑电路图                           | .48 |

| 图  | 4.16 SAR ADC 控制逻辑电路关键波形仿真图                     | .49 |

| 图  | 4.17 动态比较器蒙特卡洛 MC 仿真结果                         | .49 |

| 图  | 4.18 SAR ADC 非理想因素影响的系统 SQNR 分布直方图             | .50 |

| 图  | 4.19 bootstrap 采样开关电路图                         | .51 |

| 图  | 4.20 DWA 电路结构图                                 | .51 |

| 图  | 4.21 时钟模块电路图                                   | .52 |

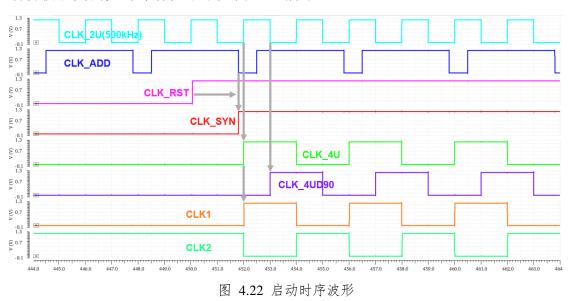

| 图  | 4.22 启动时序波形                                    | .52 |

| 图  | 5.1 系统电路 SQNR 前仿典型 FFT 输出频谱(2 <sup>14</sup> 点) | .55 |

| 图  | 5.2 系统电路 SNDR 前仿典型 FFT 输出频谱(2 <sup>14</sup> 点) | .56 |

| 图  | 5.3 系统电路前仿功耗分配                                 | .57 |

| 图  | 5.4 芯片版图设计                                     | .59 |

| 图 | 5.5 芯片照片                                       | 59 |

|---|------------------------------------------------|----|

| 图 | 5.6 系统电路 SQNR 后仿典型 FFT 输出频谱(2 <sup>14</sup> 点) | 61 |

| 图 | 5.7 系统电路 SNDR 后仿典型 FFT 输出频谱(2 <sup>14</sup> 点) | 61 |

| 图 | 5.8 系统电路后仿功耗分配                                 | 62 |

| 图 | 5.9 测试 PCB 照片                                  | 63 |

| 图 | 5.10 测试平台照片                                    | 63 |

| 图 | 5.11 芯片输出频谱测试结果(2 <sup>16</sup> 点)             | 64 |

| 图 | 5.12 芯片功耗分配测试结果                                | 65 |

| 图 | 5.13 芯片动态范围测试结果                                | 65 |

| 图 | 5.14 芯片供电电压稳定性测试结果                             | 66 |

|   |                                                |    |

| 表 | 3.1 2-0 MASH ADC 设计指标                          | 27 |

| 表 | 3.2 2-0 MASH ADC 电容取值                          | 32 |

| 表 | 5.1 芯片引脚分配                                     | 60 |

| 表 | 5.2 系统关键指标前后仿与测试结果对比                           | 65 |

| 表 | 5.3 近年来低功耗 ADC 性能对比(<10μW)                     | 67 |

## 1 绪论

#### 1.1 研究背景及意义

在如今的信息时代,包含各种信号的信息已经成为一种重要的资源。且随着集成电路技术的飞速发展以及工艺的不断进步,处理数字信号的能力越来越强大。然而,我们所处的自然界中,例如声音、图像、温度等,都是模拟信号。为了将自然界的模拟信号转化为程序可以处理的数字信号,就需要模数转换器(Analog to Digital Converter, ADC)作为中间的桥梁,因此,ADC 的重要性不言而喻。随着物联网(Internet of Things, IoT)的发展,智能传感器日益普及,生产生活中对ADC 的需求量也在逐渐上升。

在诸如 IoT 的应用场景中,往往面临着长时间稳定工作与电池供电导致电源受限的矛盾,这使得用户对功耗指标的要求愈加严苛;同时,为了保证满足分辨率需求以及适应复杂多变的应用环境,ADC 的信噪比以及工艺、电压、温度(Process Voltage Temperature, PVT)稳定性要求也越来越高。

#### 1.2 国内外研究现状

目前较为成熟的 ADC 架构可分为  $\Delta\Sigma$  ADC, 逐次逼近型(Successive Approximation, SAR) ADC, 全并行(Flash) ADC, 流水线型(Pipeline) ADC, 单斜率(Single-Slope) ADC 等。其中  $\Delta\Sigma$  ADC 与 SAR ADC 应用较为广泛: 前者适用于低速高精度应用场合,如检测装置、数字语音和音频应用等;后者适用于中速中精度应用场合,如无线传感器、生物医疗设备等。 $\Delta\Sigma$  ADC 利用过采样(Oversampling)与噪声整形(Noise Shaping, NS)技术实现较高的量化精度,它并不需要单次的高精度量化,而是通过对信号的多次粗量化实现目标,可细分为高阶(High Order)与多级(Multiple Stage)两种设计思路; SAR ADC 又被称为二进制搜索 ADC,将信号采样之后,通过逐次逼近的二进制算法实现量化。除此之外,近年来也诞生了不同种类 ADC 融合的新架构,例如 NS SAR ADC 与 Zoom ADC等。

1

本小节将着重对近年来  $\Delta\Sigma$  ADC 和 SAR ADC 这两类进行介绍。

#### 1.2.1 学术界研究现状

图 1.1 学术研究领域 FoM 性能总结

对于 ADC 而言,精度、带宽与功耗是其中关键的指标。为了科学合理地对比不同 ADC 性能的优劣,提出了品质因数(Figure of Merit, FoM)的概念来进行综合评判,目前采用较多的为 Schreier FoM。一般情况下,更高的 FoM 值代表更优秀的综合性能。图 1.1 给出了 2015-2021 年 ISSCC 会议与 VLSI 会议的 Schreier FoM 性能总结<sup>[1]</sup>。可以看出,对于高速 ADC 领域,FoM 值会呈现出逐渐下降的趋势;在中速领域,FoM 值可以逼近到 185dB 左右;在低速低功耗领域,FoM 值也会下降。

当然,仅仅 FoM 值的高低并不能完善地评判 ADC 的性能优劣,还需要考虑 具体的应用场合。例如,在高速应用场合,寄生参数的影响不可忽略;在低功耗 领域,一些辅助电路模块,例如时钟电路和缓冲器,它们是系统正常工作所必需 的,但对于精度的提高没有贡献,这些电路带来的额外功耗也会使得 FoM 值降 低。

近年来,学术界研究中,在系统架构层面上主要以融合创新为主,以此来弥补单一架构的固有缺陷。例如,研究成果产出较多的 NS SAR ADC 通过在 SAR ADC 基础上融入  $\Delta\Sigma$  ADC,有效地提高了精度<sup>[2][3][4]</sup>,除此之外 Zoom ADC 也是

结合了二者的结构<sup>[5][6][7]</sup>; 还有结合了 Pipeline ADC 与 SAR ADC 的 Pipe-SAR ADC<sup>[8] [9]</sup>以及在  $\Delta\Sigma$  ADC 结构基础上采用结合了 NS SAR ADC 与 Pipeline ADC 的 Pipe NS SAR ADC<sup>[10][11]</sup>等。

在 NS SAR ADC 研究领域,Jiaxin Liu<sup>[2]</sup>与 Tzu-Han Wang<sup>[3]</sup>在 2021 年 ISSCC 会议上发表的论文综合性能较为突出,都实现了高达 182dB 的 Schreier FoM 值。前者的创新点在于通过使用电容叠加和缓冲进行积分,避免了无源电荷分配所导致的信号衰减;并且系统中不需要闭环或开环放大器;在电路中采用简单的源跟随器实现了较好的鲁棒性以及噪声整形效果(四阶),最终在 250kHz 带宽范围内达到了 93.3dB 的 SNDR,但功耗相对较高,为 340μW。后者则通过反馈-前馈混合型结构实现了较高的噪声整形效果(三阶)以及适用于动态放大器(Dynamic Amplifier, DA)的采样 kT/C 噪声消除技术(Sampling kT/C Noise Cancellation, SNC)实现了较高的信噪比,最终在 625kHz 的带宽范围实现了 84.8dB 的 SNDR,但功耗也相对较高,为 119μW。在低功耗应用方面,NS SAR ADC 在近年来研究成果相对较少,在 2019 年 ISSCC 会议 Mario Konijnenburg 在 SoC 中实现了功耗仅为 900nW 的 NS SAR ADC<sup>[4]</sup>,但是它的信噪比指标也相对较低,在 150Hz 的带宽范围内仅为 78.8dB 的 SNDR。

相较于 NS SAR ADC, Zoom ADC 以  $\Delta\Sigma$  结构为主体,更适合低功耗、高精度应用,常用于量化频率较低的信号。对于 Zoom ADC 的研究主要集中在荷兰代尔夫特科技大学 Kofi 教授所领导的模拟集成电路设计组,主要应用包括温度、风速等传感器。在 2018 年 Shoubhik Karmakar 等人提出的高精度 Dynamic Zoom ADC<sup>[5][6]</sup>在 1KHz 的带宽范围内,实现了 118.1dB 的 SNDR,功耗为 280 $\mu$ W,从而达到了 183.6dB 的 Schreier FoM 值。

除上述的架构融合创新之外,还有在时间域结合离散时间(Discrete Time, DT) 域与连续时间(Contiuns Time, CT) 域进行融合创新的 CT- DT ADC;同时,还有结合时间域与相位域的压控振荡器(Voltage-Controlled Oscillator, VCO)ADC等。

在具体的电路设计层面,作为 ADC 关键模块的运算放大器,其设计经历了从静态运放到动态运放的转变。近年来在动态运放方面的成果主要由 Xiyuan Tang 贡献,他提出的浮动反相器运算放大器(Floating Inverter Amplifier, FIA)最早用作比较器的预放大级<sup>[12][13]</sup>,通过动态工作模式,极大地降低了功耗,同时 FIA

具有较好的 PVT 稳定性、不需要共模反馈(Common Mode Feedback, CMFB)电路的优点。在[14][15]中, FIA 分别被应用于 NS SAR ADC 与 Pipeline ADC。

通过近年来学术界研究现状可以看出架构融合这一创新方向具有广阔的发展前景,通过这种方式能够使融合架构的 ADC 在不同基础结构与设计思路之间取长补短。从具体的应用领域分类来看,NS SAR ADC 与 Pipe-SAR ADC 更适合处理相对高频的信号,但它们的精度受限于采样电容大小且具有相对较高的功耗;以  $\Delta\Sigma$  ADC 为主体的 Zoom ADC 更适用于高精度、低功耗应用。从具体的电路设计层面上来看,FIA 应用于 DT ADC 可以有效降低功耗,为低功耗研究方向开辟了新的道路。

#### 1.2.2 产业界调研

在产业界中,ADC 芯片生产厂商以亚德诺半导体(Analog Devices Inc., ADI)和德州仪器(Texas Instruments, TI)为代表。由于产业界设计需要根据客户需求和应用场合的不同,更加全面地考虑多种因素,例如适用的电源电压范围、输入阻抗、50/60Hz 干扰抑制、接口与控制逻辑等。为了适用更多的应用场合,维持系统稳定工作,产业界的芯片也往往不像学术界一样仅仅是追求某些极致指标的"裸"ADC,而是会同时集成一系列周围电路,例如控制接口、可选内部时钟、滤波器电路以及可编程增益放大器(Programmable Gain Amplifier, PGA)、保护电路等,实现完整的芯片功能。这些必要的周围电路会导致芯片的功耗升高。

AD7788 与 AD7789 是 ADI 的两款低功耗 ΔΣ ADC, 二者不同之处在于 AD7789 具有 24bit 分辨率,AD7788 则是一个 16bit 分辨率版本的 AD7789,其 余特性指标均相同,芯片内部模块如图 1.2 所示 $^{[16]}$ 。输入端等效输入噪声方均根值为  $1.5\mu$ V,在参考电压为 2.5V 时,有效分辨率上限为 21.5bit,由信号峰-峰值噪声所得分辨率上限则为 19bit。芯片的数据输出速率较低,仅为 16.6Hz,且具有 50/60Hz 的噪声抑制功能。芯片供电电压范围较宽为 2.5V 到 5.25V,在 3V 电源电压供电时,功耗仅为  $225\mu$ W。芯片功耗明显高于近年来学术界成果,其中有两个主要原因:一方面是因为芯片电源电压较高,而  $\Delta\Sigma$  ADC 在输出一个数据的工作过程中要经过多个周期的粗量化,对中间节点的充放电损失功耗与电源电压

的平方成正比;另一方面则是由于芯片功耗的计算不仅包含 ADC 模块,还包含了时钟与串行接口和控制逻辑等电路。

#### **FUNCTIONAL BLOCK DIAGRAM**

图 1.2 AD7788/7789 功能框图

#### Simple 24-Bit 2-Speed Acquisition System

图 1.3 LTC2440 典型应用

TLA202x 系列芯片是 TI 公司的低功耗 12bit  $\Delta\Sigma$  ADC 产品,其典型应用如图 1.4 所示[18]。系统功耗低至 150 $\mu$ A,供电电压范围为 2V 到 5.5V,输出数据速率

可以在 128SPS 到 3.3kSPS 共七个档位之间选择。与前述的 AD7788/9 和 LTC2240 在结构上的最大不同之处在于该芯片内部集成了 PGA, 可以实现从±256 mV 到 ±6.144 V 的信号测量。但是, TLA202x 并未给出输入端等效噪声均方根值大小, 而是给出了在 PGA 处于不同档位时的满幅范围与 LSB 大小, 例如在满量程(Full Scale Range, FSR)输入为 $\pm 256$ mV 时,LSB =  $(2\times256$ mV)/ $2^{12}$  = 0.125mV。

# AIN2 TLA2024 Copyright © 2017, Texas Instruments Incorpora

#### System-Monitoring Application Example

图 1.4 TLA202x 典型应用

通过产业界调研可知,为了能够确保 ADC 的应用范围较广,需要进行多方 面的考量,例如需要采用较高的供电电压并配套较为全面的片内集成模块。考虑 到本文偏重于研究,主要目标在于设计高精度、低功耗的 ADC, 所以芯片内部 仅包含 ADC,参考电压驱动与抗混叠滤波器等均选择在片外实现,同时不考虑 较宽的供电电压范围。

#### 1.3 论文内容及结构安排

本论文的主要研究内容是针对低频信号提出的  $\Delta\Sigma$  ADC, 广泛适用于各种传 感器接口电路中。在传统的低失真(Low - distortion)前馈型级联积分器(Cascade of integrators with feed forward, CIFF)结构的基础上,提出采用 SAR ADC 将前馈通 路由模拟域转为数字域,不仅缓解了环路中积分器的饱和压力,也使得电容型反 馈数模转换模块(Digital to Analog Converter, DAC)从一位变成了多位,从而有效 地降低了功耗。同时,通过对上述 SAR ADC 进行时分复用,使其构成了 MASH ADC 的第二级,在节约版图面积基础上,消除了前级的量化噪声。在电路设计

层面上,结合了浮动反相放大器与相关电平偏移(Correlated Level Shift, CLS),并创新地利用了体效应(Body Effect)进行控制,实现了单级高增益低功耗运算放大器。芯片在 TSMC 55nm CMOS 工艺下完成设计,并进行了流片验证和测试。

本论文共分为六章,以下为论文的结构安排:

第1章为绪论。介绍了本文的研究背景,并对当前学术界和产业界的研究发展状况进行了调研总结,提出了论文的主要研究内容;

第 2 章为 MASH ADC 的相关基础知识。介绍了  $\Delta\Sigma$  ADC 的工作原理,对 MASH ADC 的基本原理及其发展过程进行了研究与分析;

第3章为系统架构和理论分析。介绍了本文提出的系统架构与相关关键技术, 给出在系统层面的仿真结果,提出了对模块电路的指标要求:

第 4 章为系统模块电路设计。介绍了各模块的设计思路与结构及工作原理,对本文提出的结合 CLS 与 FIA 技术的动态体偏置放大器进行了着重分析,对 SAR 量化器、升压开关、动态元件匹配(Dynamic element matching, DEM)模块和时钟模块进行了原理分析,并在此基础上进行了电路设计,最后给出了模块电路的仿真结果:

第5章为版图设计以及仿真和测试结果。介绍了版图布局思路,比较了前仿与后仿结果,并给出了系统的典型频谱分析、动态范围、电源电压变化的测试结果并进行了分析;

第6章为总结与展望。总结了本论文设计中的优势及不足之处,给出了进一步的优化方向,展望了低功耗 ADC 研究领域未来的发展方向。

## 2 MASH ADC 技术基础

$\Delta\Sigma$  ADC 的噪声整形效果随其阶数升高而变好,然而过高的阶数,例如三阶及以上,会不可避免地导致积分器与量化器饱和从而引起稳定性问题,因此,近年来的  $\Delta\Sigma$  ADC 主要为二到三阶。为了解决这一问题, $\Delta\Sigma$  ADC 转向了另一种设计思路,通过多级设计来实现更高的精度。

#### 2.1 ADC 技术指标

为了更好地描述不同 ADC 的性能以及适用场景,ADC 采用了多种技术指标。这些技术指标大致可以被分为四类,分别是基本特性参数、静态性能参数、动态性能参数、数字和开关性能指标。关于这些性能指标,在 Franco 的《数据转换器》<sup>[19]</sup>以及 Schreier 的《Understanding Delta-Sigma Data Converters》<sup>[20]</sup>书中有着详细的介绍。在本小节中,仅对其中较为重要的指标进行总结与解释。

#### 2.1.1 基本特性参数

#### 1. 模拟信号类型

ADC 的模拟输入/输出可以分为单端型、伪差分型以及全差分型。它们的区别在于输入/输出信号与参考电压之间的关系不同。

#### 2. 精度

ADC 用于表示其模拟输入的位数,或者是 DAC 在其输入端接收到的用于转换成模拟量的位数。同时,该参数也表示 ADC 输入端可检测的最小电压,或者是 DAC 输出的最小变化量,由精度和参考电压 V<sub>REF</sub> 共同决定。其中参考电压通常与系统供电电压相等。

#### 3. 动态范围(Dynamic Range, DR)

ADC 所能处理的最大电压与噪声电压的比值,用分贝 dB 表示。动态范围决定了最大信噪比。

#### 2.1.2 静态性能参数

#### 1.模拟分辨率

ADC 所能分辨的最小模拟增量,也就是 1 个最低有效位(Least Significant Bit, LSB)。对于一个精度为 N 位的 ADC 而言,它可以表示  $2^N$  种输出状态,可以得出此时 LSB 与参考电压  $V_{REF}$  的关系为: LSB =  $V_{REF}/2^N$

#### 2.功耗

通常可以分为两种类型,芯片在正常工作状态或待机(或着掉电)状态下的所消耗的功率。值得注意的是,若芯片供电引脚不止一个,例如模拟电源/数字电源/参考电压电源等,则应计算其功耗总和。

#### 2.1.3 动态性能参数

1.信号-量化噪声比(Signal-to-Quantization Noise Ratio, SQNR)

信号能量与量化噪声(Quantization Noise)的能量比值。量化噪声指在理想情况下,由于量化器有限量化精度造成的量化结果与输入值之间的差异。量化噪声随着 LSB 的增大而增大。

2.信号-噪声比(Signal-to-Noise Ratio, SNR)

信号能量与由量化噪声和电路噪声引起的总噪声能量之比。由于制造成本原因,通常情况下在  $\Delta\Sigma$  ADC 的设计中,量化噪声远低于电路噪声;而在电路噪声中,热噪声占据主导地位。

3. 信号-噪声失真比(Signal-to-Noise-and-Distortion Ratio, SINAD or SNDR)

信号能量与噪声能量及非线性失真的能量和的比值。由于静态和动态特性限制所导致的系统非线性响应,会产生与输入信号幅度及频率相关的谐波失真(Harmonic Distortion, HD)。因此, SNDR 会低于 SNR。

4. 无杂散动态范围(Spurious Free Dynamic Range, SFDR)

信号幅值的方均根值与第一奈奎斯特区间中最大杂散频谱分量的方均根值的比值。在此,SFDR关注的是最坏的谐波分量。

#### 5.动态范围

当输入信号为 0dB 时的信噪比,或者信噪失真比为 0 时输入信号的值。这对于无法在 0dBFS 输入时得到最大 SN(D)R 的 ADC 非常有用,例如  $\Delta\Sigma$  ADC。

因此,本文采用的定义为后者。

#### 6.有效位数(Effective Number of Bits, ENOB)

用来描述 ADC 量化精度的二进制数的位数,与 SNDR 有关,计算公式如下 所示:

$$ENOB = \frac{SNDR - 1.76}{6.02} \tag{1.1}$$

#### 7.品质因数(FoM)

衡量 ADC 功耗效能的一个参数,它综合考量了 ADC 的总功率消耗、带宽 (Bandwidth, BW)、等效位数。有多种 FoM 指标,较常见的为 Schreier FoM,表达式为

$$FoM_{SNDR} = SNDR + 10log_{10}(\frac{BW}{Power})$$

(1.2)

$$FoM_{DR} = DR + 10log_{10}(\frac{BW}{Power})$$

(1.3)

#### 2.1.4 数字和开关性能指标

#### 1. 逻辑电平(Logic Levels)

幅值不重叠的一系列电压区间,用来表征不同的逻辑状态,所使用的逻辑电平要保证与定义的逻辑标准相符。

#### 2. 休眠模式

定义省电模式。通过关掉偏置电流或部分电路来减小功耗。

#### **2.2** ΔΣ ADC 基本理论

$\Delta\Sigma$  ADC 属于过采样 ADC, 主要通过过采样与噪声整形来提高信噪比。通常情况下,过采样率(Oversampling Rate, OSR)的典型值为 8 到 512 之间的一个系数 [20],这使得关注的信号带宽会远小于奈奎斯特频率,从而降低带内噪声。噪声整形技术则是通过环路滤波器将近似白噪声的量化噪声频谱进行整形,从而进一步减小带内量化噪声,获得更高的信噪比。

#### 2.2.1 量化噪声

量化是指将连续模拟输入转化为离散数字输出的过程,是非线性且无记忆的数据转换。最简单的量化器即为比较器,将两模拟输入的大小关系转换为 0 或 1 输出的数字值。典型的量化器输入-输出曲线如图 2.1 所示,横轴为输入信号 y,纵轴为量化结果 v,量化结果与输入信号的差值即为量化误差 e。可以看到,量化结果为包络输入信号的阶梯型曲线,更高位数的量化器可以实现更密的量化阶梯,也意味着更小的量化误差 e。图 2.1(a)和(b)两种量化方式的区别在于 0 输入时对应的是阶梯的平台还是上升沿。

图 2.1 量化器输入-输出曲线

量化噪声的概念往往被用来近似表示量化误差 e 在量化操作中的影响。从图中可以看出量化误差是输入值的一个复杂函数,在量化器非饱和区间内为锯齿型曲线。量化器的这种非线性使得工程师们对量化误差的性质做了一些假设,即信号大小处于非饱和区间内且两次信号之间变化足够大。在[21]中,给出了更加详细的四个假设:

- 1.假设 e 是一个可加的噪声序列;

- 2.假设 e 与输入信号 v 不相关:

- 3.假设 e 在[-1,1]之间均匀分布;

- 4.假设 e 是白噪声。

尽管上述四个假设很难满足,但仍旧可以在此基础上对量化噪声进行简单的近似估算。假设量化器的量化间隔为 $\Delta$ ,那么对于任意输入信号,量化噪声 e 将在 $[-\Delta/2, \Delta/2]$ 之间均匀分布,所以量化噪声的功率平均值可以近似为:

$$P_Q = \int_{-\Delta/2}^{\Delta/2} e^2 \, de = \frac{\Delta^2}{12} \tag{2.1}$$

#### 2.2.2 过采样

根据香农采样定理,为了能够不失真地恢复模拟信号,采样频率  $f_S$  应当大于等于模拟信号频谱中最高频率  $f_B$  即奈奎斯特频率的两倍。SAR ADC 与 Pipeline ADC 等奈奎斯特型 ADC 的信号带宽  $f_B$  为采样频率  $f_S$  的一半,而  $\Delta\Sigma$  ADC 则不同,其  $f_B$  经过过采样技术会降低。过采样率 OSR 的定义为奈奎斯特频率  $f_N$  与信号带宽  $f_B$  的比值,则  $f_B$  与  $f_S$  的关系可表示为:

$$f_B = \frac{f_S}{2*OSR} \tag{2.2}$$

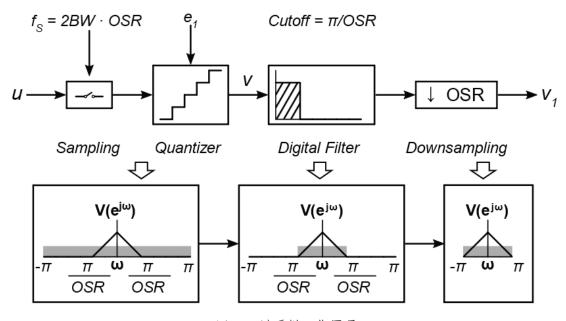

过采样技术对量化噪声的影响如图 2.2 所示。在频域中,量化噪声均匀地分布在 $[-\pi,+\pi]$ 区间内,由式(2.1)可知噪声密度为  $\Delta^2/(24\pi)$ ,在量化器之后通过数字滤波器,可以将 $[-\pi/OSR,+\pi/OSR]$ 区间之外的量化噪声全部滤除,然后再通过降采样环节恢复信号。通过这种方式,可以极大地降低量化噪声,即过采样率每提高一倍,带内量化噪声缩小为原先的 1/2,SQNR 提高 3dB,分辨率提高 0.5bit。

图 2.2 过采样工作原理

#### 2.2.3 噪声整形

由前两小节可知,量化器位数提高和过采样率提高都可以提高 ADC 最终的分辨率。但这两种方式都会受到限制,更高位数的量化器会受到器件失配的影响;

而更高的采样率则意味着在信号带宽不变的情况下提高采样频率,这需要更高的时钟频率,会导致系统的功耗升高,同时也需要让系统在更短的周期内完成转换工作,例如采样、积分和比较过程的时间都会缩短。种种限制使得在实际设计中不能仅靠这两种方式进一步降低量化噪声,所以在过采样的基础上, $\Delta\Sigma$ ADC中又引入了噪声整形技术。

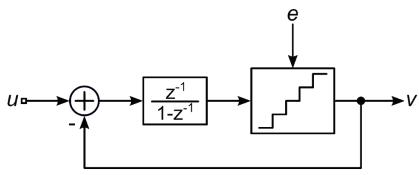

图 2.3 一阶 ΔΣ ADC 结构框图

典型的一阶  $\Delta\Sigma$  ADC 框图如图 2.3 所示。可以得到输出信号  $\nu$  的表达式为:

$$V(z) = STF \cdot U(z) + NTF \cdot E(z) = z^{-1} \cdot U(z) + (1 - z^{-1}) \cdot E(z) \quad (2.3)$$

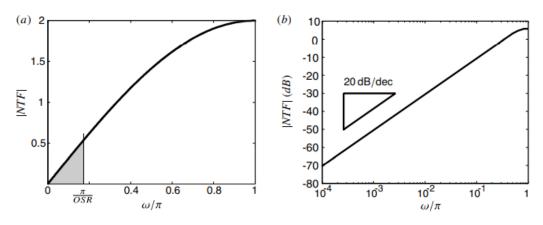

式中信号传递函数(Signal Transfer Function, STF)为  $z^{-1}$ ,代表系统输出仅为一个周期延时的输入;噪声传递函数(Noise Transfer Function, NTF)为( $1-z^{-1}$ ),代表量化噪声经过了高通滤波的处理。以采样频率  $f_s$  为基准进行归一化处理,此时一阶 $\Delta\Sigma$  ADC 的频域噪声整形效果如图 2.4 所示,其中(a)图横坐标与纵坐标均为线性坐标,(b)图为横坐标频率取对数坐标,纵坐标单位取 dB。通过(b)图可以看到一阶噪声整形的高通滤波效果具有 20dB/decade 的斜率。

图 2.4 一阶 ΔΣ ADC 频域噪声整形<sup>[20]</sup>

对带内噪声(Inband Noise, IBN)积分可以得到:

$$IBN = \frac{\Delta^2}{24\pi} \int_{-\frac{\pi}{OSR}}^{+\frac{\pi}{OSR}} \left| 1 - e^{-j\omega} \right|^2 d\omega = \frac{\Delta^2}{12\pi} \int_{0}^{+\frac{\pi}{OSR}} 4 sin^2 \left( \frac{\omega}{2} \right) d\omega$$

$$\approx \frac{\Delta^2}{12\pi} \int_0^{+\frac{\pi}{OSR}} \omega^2 d\omega = \frac{\Delta^2}{36\pi} \frac{\pi^3}{OSR^3}$$

(2.3)

通过该积分结果可知, IBN与OSR<sup>3</sup>成反比,即OSR每升高一倍,SQNR可以提高9dB,分辨率提高1.5bit。需要注意的是,全频带内的噪声总量经过NTF噪声整形之后会升高,所以噪声整形技术必须结合过采样技术一起使用。

#### 2.2.4 二阶 ΔΣ ADC

通过前一小节可知, $\Delta\Sigma$  ADC 在过采样技术基础上利用噪声整形技术,可以进一步降低带内噪声,而为了获得更好的噪声整形效果,可以采用更高阶的  $\Delta\Sigma$  ADC,即增加级联积分器的数量。以典型的二阶  $\Delta\Sigma$  ADC 为例,如图 2.5 所示。

图 2.5 二阶 ΔΣ ADC 结构框图

可以得到输出信号ν的表达式为:

$V(z) = STF \cdot U(z) + NTF \cdot E(z) = z^{-1} \cdot U(z) + (1 - z^{-1})^2 \cdot E(z)$  (2.4) 在较低频段, NTF 的幅值可以近似为  $\omega^2$ , 因此, 对带内噪声积分可得:

IBN

$$\approx \frac{\Delta^2}{12\pi} \int_0^{+\frac{\pi}{OSR}} \omega^4 d\omega = \frac{\Delta^2}{60\pi} \frac{\pi^5}{OSR^5}$$

(2.5)

从式中可以看出带内噪声总量与 OSR<sup>5</sup> 成反比,即 OSR 每提高一倍,SQNR 可以提高 15dB,分辨率可以提高 2.5bit。与一阶噪声整形相比,二阶的过采样效果有了很大的改善。

由理论分析可知,随着阶数的升高,噪声整形效果会越来越好,但在实际设计中并不能无限地提高阶数。原因是在电路中积分器和量化器所能处理的信号幅值有限,其取决于运放的输出摆幅等因素。随着阶数的升高,噪声的总能量也会随之升高,同时,环路中积分器和量化器更容易出现饱和现象,从而导致 ADC 无法处理较大幅值的输入信号,使得实际能够实现的信噪比降低。所以目前较为常见的  $\Delta\Sigma$  ADC 多为二阶或三阶。

应用较多的 CIFF 低扰动结构  $\Delta\Sigma$  ADC 结构如图 2.6 所示[22][23]。可以得到输出信号的表达式为:

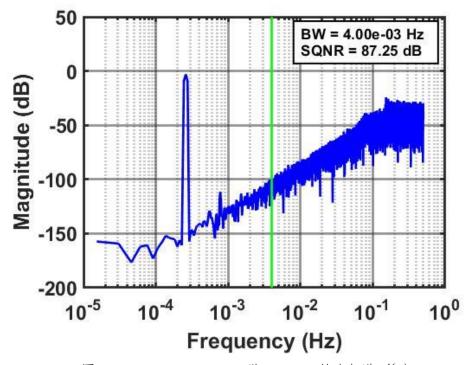

$V(z) = STF \cdot U(z) + NTF \cdot E(z) = U(z) + (1-z^{-1})^2 \cdot E(z)$  (2.6) 该结构通过前馈环路将输入信号直接叠加到量化器输入端。通过这种方式,环路中的积分器仅需要处理误差信号,从而减小了积分器饱和的压力。在不考虑积分器输出摆幅的情况下,其 MATLAB 代码仿真结果如图 2.7 所示。仿真条件为 OSR=125,对信号频率进行归一化处理,输入信号幅值为 0.7 倍的满幅,即-3dBFS,仿真点数为  $2^{16} = 65536$  点。可以看到仿真结果中具有明显的二次整形效果,信号量化噪声比 SQNR = 87.25dB。

图 2.6 Silva-Steensgaard 二阶 ΔΣ ADC

图 2.7 Silva-Steensgaard 二阶 ΔΣ ADC 输出频谱(2<sup>16</sup>点)

#### 2.3 MASH ADC 的工作原理

由 2.2 节已知, ΔΣ ADC 通过噪声整形与过采样技术可以减小量化噪声, 然而过高的阶数会带来系统稳定性的问题。为了解决这一问题, 人们把研究方向从高阶设计转向了多级设计。

#### 2.3.1 多级 ADC 拓扑结构与信号分析

典型的多级  $\Delta\Sigma$  ADC 拓扑 Lesli-Singh 结构如图 2.8 所示<sup>[24]</sup>。其中第一级环路可以为任意阶数  $\Delta\Sigma$  ADC。其核心思路为提取出第一级量化误差  $e_I$ ,并将其送入第二级 ADC 进行量化,随后通过传递函数匹配并做差,使得最终的输出信号v 中不含  $e_I$ ,达到进一步减小量化噪声的效果。

图 2.8 Lesli-Singh 结构框图

在图 2.8 中,经过传递函数匹配做差,在输出信号中原先第一级量化误差  $e_1$  被转换为第二级量化误差  $e_2$ ,但  $e_2$  可以远远小于  $e_1$ ,其原因是第二级 ADC 不在  $\Delta\Sigma$  环路中,使得它可以具有任意的延时。在这种情况下第二级 ADC 可以采用例 如多 bit Pipeline ADC 以减小量化误差。

通常情况下, $H_1=z^{-k}$ ,这仅仅只是一个第二级 ADC 的延时; $H_2$  取值则为第一级的 NTF。此时将  $H_1$  和  $H_2$  的输出做差可以得到最终的输出  $\nu$ ,即:

$$V(z) = H_1(z)V_1(z) - H_2(z)V_2(z)$$

$$= z^{-k}[STF_1(z)U(z) + NTF_1(z)E_1(z)] - NTF_1(z)z^{-k}[E_1(z) + E_2(z)]$$

$$= z^{-k}[STF_1(z)U(z) - NTF_1(z)E_2(z)]$$

(2.7)

需要注意的是为了提取出第一级的量化误差 e1,需要对量化器前后的信号进

行做差,要求积分器的输出  $y_1$  必须要延时到做差结束为止,这对系统的工作时序提出了更复杂的要求。一个解决方案是直接将积分器输出  $y_1$  直接送入第二级 ADC,并对数据处理环节  $H_1$ 、 $H_2$ 进行对应调整。但此时  $y_1$  中除了量化误差  $e_1$ 之外,还含有信号分量 u,所以第二级 ADC 需要能够处理更大幅值的输入信号,并且需要较低的扰动,以避免产生信号相关的谐波。

而在图 2.6 所示的 CIFF 结构中,通过对信号进行分析,可以得到在这种结构中,第二级积分器的输出为  $\mathbf{z}^{-2}\mathbf{E}_{\mathbf{l}}(\mathbf{z})$ 。这表明第二级积分器的输出为量化误差的一个延时信号。此时,积分器的直接输出更适合直接用作第二级 ADC 的输入[25]。

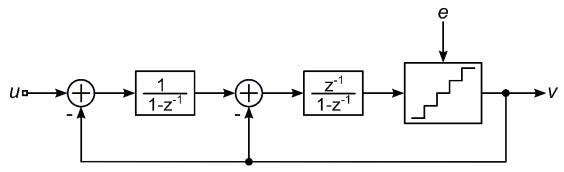

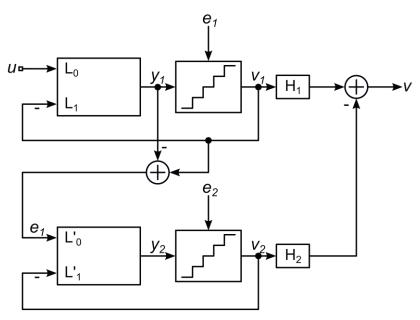

#### 2.3.2 MASH ADC 信号分析

若第二级 ADC 同样采用具有噪声整形作用的  $\Delta\Sigma$  ADC,就变成了多级噪声整形 (Multi-stage Noise Shaping, MASH) 结构,如图 2.9 所示。此时,可以得到第一级量化器与第二级量化器输出分别为:

$$V_1(z) = STF_1(z)U(z) + NTF_1(z)E_1(z)$$

(2.8)

$$V_2(z) = STF_2(z)E_1(z) + NTF_2(z)E_2(z)$$

(2.9)

为了能够将输出信号 $\nu$ 中的第一级量化误差 $e_l$ 完全消除, $H_1$ 和  $H_2$ 应满足:

$$H_1 \cdot NTF_1 = H_2 \cdot STF_2 \tag{2.10}$$

一个较为简单的实现方式为 $H_1=STF_2$ , $H_2=NTF_1$ ,此时可得输出信号为:

$$V = H_1 V_1 - H_2 V_2 = STF_1 STF_2 \cdot U - NTF_1 NTF_2 \cdot E_2 \tag{2.11}$$

假设两级 ADC 均为常见的二阶  $\Delta\Sigma$  结构,可得:

$$STF_1(z) = STF_2(z) = z^{-2}$$

(2.12)

$$NTF_1(z) = NTF_2(z) = (1 - z^1)^{-2}$$

(2.13)

$$V(z) = z^{-4} \cdot U(z) - (1 - z^{-1})^4 E_2(z)$$

(2.14)

图 2.9 MASH ADC 结构框图

由式(2.14)可知,二级 MASH 结构可以通过两个二阶  $\Delta\Sigma$  ADC 可以实现四阶噪声整形效果,而稳定性要求仍旧为二阶,并不会额外增加。所以 MASH ADC 可以实现更好的噪声整形效果,同时不会引入由饱和带来的环路稳定性问题。

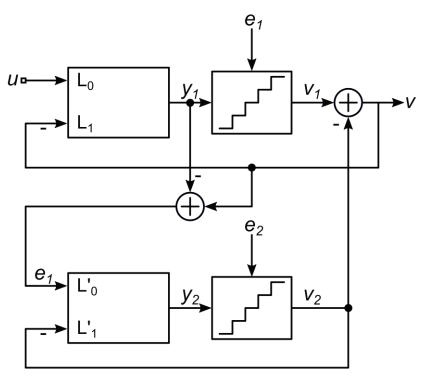

#### **2.3.3 SMASH ADC**

然而,在电路实现过程中,作为积分器核心的运算放大器增益不可能是理想的,有限的增益与线性度在 MASH 结构中会导致噪声泄露的问题,从而导致没能完全消除的量化误差直接出现在输出信号中,因此,它通常对运放的增益以及电容的匹配具有比较高的要求 $^{[26]}$ 。为了解决这一问题,U.Moon等人提出了 Sturdy MASH(SMASH)结构 $^{[27]}$ ,如图 2.10 所示。其核心思路是将第二级的对  $e_I$  的量化结果重新送回第一级环路,并选择合适的 STF2,这样就不再要求数字域的  $H_1$  与  $H_2$  与模拟域的传递函数精确匹配,所以系统对运放增益的要求变低,而作为代价的是其最终信噪比损失了 3dB。 SMASH 的架构在此后也不断有改进,例如 Delay based Noise Cancelling SMASH $^{[28]}$ 与 Noise Cancelling SMASH $^{[29]}$ ,前者在环路中插入延时并增加了反馈路径,后者则是在 SMASH 基础上重新加入了数字滤波环节,二者都实现了在最终量化结果中消除量化误差  $e_I$ 。

图 2.10 SMASH ADC 结构框图

#### **2.3.4 Zoom ADC**

在 Leslie-Singh 结构的基础上,若将 SAR ADC 置于  $\Delta\Sigma$  ADC 环路前,就形成了 Zoom ADC。2018 年,Kofi 等人提出了典型的 Zoom ADC 结构,如图 2.11 所示[5][6]。和 MASH 结构相比,Zoom ADC 中的  $\Delta\Sigma$  环路负责处理 SAR 的量化误差,这一思路与 MASH ADC 相似,若将 MASH 结构视作没有噪声整形效果的零阶  $\Delta\Sigma$  ADC,则 Zoom ADC 可以被分类为 0-n MASH。与此同时,由于 SAR ADC 的量化误差远小于输入信号,积分器与量化器的饱和问题得以有效缓解。另一方面,在结合 SAR 的量化结果与  $\Delta\Sigma$  环路的量化结果时,由于 STF $\Delta\Sigma\neq 1$ ,在 OSR 较高,信号带宽较窄的情况下,对量化精度影响不大,但在高频区域会有"fuzz"的产生。[5][6]给出的解决方案是对 SAR 的量化结果添加 STF 的数字滤波后,再进行数据的结合,这种方法同样会依赖数字滤波与模拟传递函数的精确匹配。针对这一问题,[7]给出的解决方案是增添前馈通路,这种方式的代价是引入了新的 DAC,从而使得功耗和面积开销变大。

在  $Zoom\ ADC$  中,由于信号已经经过了粗量化,所以可以缩小反馈电压的范围,这种工作模式与采用多位量化器的单级  $\Delta\Sigma\ ADC$  类似,此时,由于积分器输出信号摆幅进一步减小,功耗也随之降低。需要注意的是,在开关电容电路中,

为了反馈不同的电压常采用的 CDAC 反馈,即将反馈电容划分为同样容值的小单位电容。由于工艺误差等影响,会引入失配噪声  $Q_M$ 。在系统层面上, $Q_M$ 与输入信号在相同的位置引入,所以需要 DEM 模块对  $Q_M$  进行处理,在 2.5 节对此进行了详细的分析。

图 2.11 Zoom ADC 结构框图

#### 2.4 积分器

噪声整形是  $\Delta\Sigma$  ADC 降低量化噪声的主要技术之一,其在频域中体现为将量化噪声进行高通滤波,在时域中则体现为记录前一次的量化误差,并在下一次量化过程中减去。在电路层面上噪声整形通过积分器实现。因此,可以说积分器是 $\Delta\Sigma$  ADC 中最为重要的部分。根据其在时域的工作方式不同可以分为传统的 DT积分器与近年来兴起的 CT 积分器。

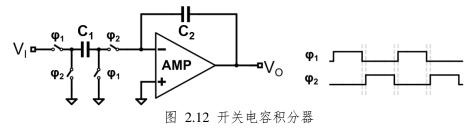

#### 2.4.1 积分器传递函数

DT 积分器由开关电容方式实现,典型电路如图 2.12 所示,其中  $\phi_1$  和  $\phi_2$  为非交叠时钟。

在  $\varphi_1$  相位,采样电容  $C_1$  对输入信号  $V_1$  进行采样,此时积分电容  $C_2$  上保留上一个周期的输出值,则有:

$$q_1[n] = C_1 v_i[n] (2.15)$$

$$q_2[n] = C_2 v_o[n] (2.16)$$

在  $\varphi_2$  相位,采样电容  $C_1$  左端由输入电压切换为共模地电位,右端与运放反向输入端相连,此时由于反馈及运放的虚短特性,使得在  $\varphi_1$  采样电容所采集到的电荷完全转移至积分电容上,即:

$$q_2[n+1] = q_2[n] + q_1[n] (2.17)$$

将式(2.15)和式(2.16)代入式(2.17),并进行 z 变换,可得:

$$\frac{Q_2(z)}{Q_1(z)} = \frac{z^{-1}}{1 - z^{-1}} \tag{2.18}$$

$$\frac{V_o(z)}{V_i(z)} = \frac{C_1}{C_2} \frac{z^{-1}}{1 - z^{-1}}$$

(2.19)

式(2.19)中忽略运放的有限增益影响与寄生电容影响,其中  $C_1/C_2$  代表由采样电容和积分电容比值设置的闭环增益, $z^{-1}$  代表一个周期的延时, $1/(1-z^{-1})$ 代表无延时的积分环节。

CT型积分器主要实现方式可分为两大类,一是有源RC积分器,如图2.13(a)(b) 所示的 Opamp-RC 型与 OTA-RC 型; 二是 Gm-C 型积分器,如图2.13(c)所示。 其中 Gm-C 型具有速度优势和方便级联的优点,但由于其线性程度较差,所以它只在速度为主要考虑因素时才会采用。Opamp-RC 型与 OTA-RC 型积分器在理想情况下的传递函数均为:

从输入阻抗来看,若采用 DT 型积分器作为芯片输入端,则在其采样相位从输入端看到的电阻过小,因此需要信号源与参考电压源具有较强的驱动能力,这会使得它们耗费较大的功耗。同时,在输入端可能还需要一阶抗混叠滤波器以防

止混叠以及在带外信号较大时出现的过载。而采用 CT 型积分器通常不需要抗混叠滤波器,并且从输入端看到的阻抗较大,易于驱动。

从匹配性来看,由于 DT 型积分器由开关电容实现,其系数取决于电容的相对比值,这在芯片中可以做到相对准确;而 CT 型积分器系数与电阻或电容的绝对值有关,因此会有较大的寄生影响和工艺偏差,从而导致系统的零极点漂移影响系统的稳定性<sup>[30]</sup>。

从系统延时来看,DT 型积分器由系统时钟控制,相对较为精确,在对积分器建立时间留有设计裕量的情况下,时钟信号的轻微变化对系统影响可以忽略。而 CT 型积分器虽然从传递函数分析可以视作整周期的延时,但是由于时钟不同步所产生的额外环路延时会导致信噪比下降甚至系统的不稳定,所以可能需要考虑环路延时补偿[31][32]。

考虑到 DT 型积分器的增益可以设置得较为准确,并且其延时由系统时钟控制更加简单和精准,而 CT型积分器需要较多地考虑寄生参数与工艺误差的影响,所以本文拟采用 DT 型积分器。针对其输入阻抗不足的固有缺陷,将在 PCB 上采用电压缓冲器进行弥补。

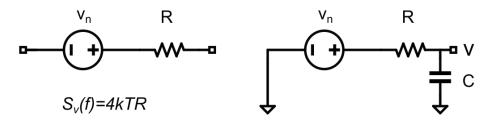

#### 2.4.2 开关电容电路噪声分析

对于开关电容电路而言,其开关通常用 MOS 管实现,在导通情况下,等效为一个导通电阻 R。其热噪声模型可以用理想电阻与一个串联电压源等效。如图 2.14(a)所示,其中噪声电压为白噪声,功率谱密度为:

$$S_v(f) = 4kTR (2.21)$$

式中,  $k = 1.38 \times 10^{-23} \text{ J/K}$ , 为玻尔兹曼常数, T 为开尔文温度。

(a) 导通时 MOS 开关的噪声模型

(b) 开关电容电路噪声模型

图 2.14 导通时 MOS 开关的噪声模型和开关电容电路噪声模型

以图 2.12 所示的开关电容积分器为例,在采样环节,可以将两个开关合在一起视作一个 R,输出端噪声电压为电压源经过了一阶 RC 滤波,如图 2.14(b)所

示。在输出端看到的功率谱密度为:

$$S_v(f) = \frac{4kTR}{1 + (2\pi fRC)^2}$$

(2.22)

对输出噪声功率谱密度在带宽内进行积分可得:

$$\overline{v_n^2} = \int_0^\infty S_v(f)df = \frac{kT}{C}$$

(2.23)

从式(2.22)~(2.23)中可以发现,由于噪声电压大小与R成正比,带宽与R成反比,所以噪声积分后不含R,仅与采样电容大小C有关。在积分相位若不考虑运放输出端的噪声,则会产生同样大的噪声电压。因此,开关电容电路中最终会有 2kT/C 的热噪声,若想降低带宽内的热噪声,只能通过增大采样电容的方式实现,这需要更大的芯片面积,也就意味着更高的成本。

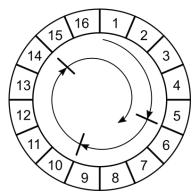

# 2.5 动态元件匹配

在本章的前几小节中主要讨论了由于量化结果与输入结果的不同带来的量化噪声  $Q_N$ 。然而在实际的  $\Delta\Sigma$  环路中,量化器输出的数字值结果在反馈时还需要经过 DAC 才能在输入端进行做差,在这个 DAC 中也同样会引入失配噪声  $Q_M$ 。采用多 bit 量化器可以有效降低输出的量化噪声,此时, $Q_M$  就有可能成为主要的限制因素。另一方面,DAC 引入噪声  $Q_M$  的位置与信号 u 的输入位置相同,这会导致其未经整形就出现在输出端。所以,在高精度  $\Delta\Sigma$  ADC 中的  $Q_M$  不可忽略。

产生 QM 的主要原因为器件的失配,例如采用电容反馈时,将电容等分为若干个相同容值的单位电容,然后通过调整其接入电路的数量不同来反馈不同的电压值。然而,实际的电容值由于工艺误差带来的失配等因素的影响,无法保证每个小电容完全相同,因此就会在 DAC 中引入失配噪声。

对于 CDAC 而言,假设将 DAC 分为  $2^N$ 个小电容,其中 1 个电容由于失配较正常值偏大,在此假设该失配电容为第  $2^{N-1}+1$  个电容。这时,每当需要反馈大于 0.5 倍满幅的信号时,就会用到这个电容,从而导致反馈信号偏大。若输入信号为某单一频率正弦波,且该失配电容参与反馈过程,就会导致  $Q_M$  叠加在输入端。由于  $Q_M$  与输入信号频率有关,因此它在对输出信号频域分析分析中,表现为谐波的形式,这会对 SNDR 产生较大的影响。

处理无源器件失配的方法主要分为两种,分别是校正和 DEM。前者主要与工

艺和制造流程相关,包括激光微调和数字芯片校准等。后者则是芯片设计者的工作,即通过算法来抑制失配带来的影响。较为常见的算法有两种,分别是随机选择法(Random selection)与数据加权平均法(Data-weighted Average, DWA)。

#### 2.5.1 随机选择法

随机选择法是通过随机选择的方式,打乱内部电容选择的顺序,使得 Q<sub>M</sub> 与输入信号无关,从而抑制谐波并提高 SNDR。这种方法由 L. Carley 在 1989 年首次提出<sup>[33]</sup>。但对于电路而言,产生真正的随机数是十分困难的,该文献采用了"蝴蝶型随机数发生器"大大简化了随机电路。

对于这种随机选择法,[34]在做出三条合理假设的前提下分析了其噪声能量,这三条假设分别是:

- 1.所选单元的所有组合具有相同的概率;

- 2.权重  $w_i$  是期望值  $E(w_i) = 1$  和方差  $sw^2$  的随机变量;

- 3.在 i≠j 的情况下,  $w_i$  和  $w_i$  无关。

因此所有单元都具有相同的概率密度函数,此时,由失配带来的误差与所选单元 无关,可得:

$$E\{y_{mis}^{2}\} = E\left\{ \left[ \sum_{i=0}^{x-1} w_{i} - \frac{x}{N} \cdot \sum_{i=0}^{N-1} w_{i} \right]^{2} \right\} = N \cdot \frac{x}{N} \cdot \left( 1 - \frac{x}{N} \right) \cdot \sigma_{w}^{2} \quad (2.24)$$

式中,N代表器件总数,x为输入DAC的数字值,即反馈的数字量。可以看到在 x=0 或者 x=N 时,误差能量最小,为0;在 x=N/2 时,误差能量最大。由于在随机选择法中,两次选择之间不同单元选择概率相同,失配噪声频谱为白噪声。

通过随机选择法,可以将谐波分量打散为白噪声,以噪底的提高为代价抑制谐波分量。通过与过采样技术的结合,可以有效降低带内的失配噪声。

### 2.5.2 数据加权平均法

如前所述,在  $\Delta\Sigma$  ADC 的实现中,可以发现仅由过采样技术降低量化噪声效果不够理想,它与噪声整形技术相结合可以更有力地降低带内量化噪声。在处理失配噪声  $Q_M$  时,也可以采用相同的思路。若某次环路中引入了误差项 ee,那么在下一次环路中就通过引入符号相反大小相同的-ee 将其消除。

由式(2.24)可知, 在 x=0 和 x=N 时引入误差能量为 0, 即若采用了全部的电

容,则引入误差能量为 0。假设在 t=0 时刻采用了 v[0]个电容,在下一个周期 t=1 时,需要用 v[1]个电容,那么为了弥补之前的误差,这 v[1]个电容应当从还未采用过的电容中挑选,即可以选用 v[0]+1 到 v[0]+v[1]之间的电容。在 t=2 周期时,继续向后顺延,直至用完所有的电容为止。若某次已用到末尾的边界电容,则可以从第一个电容重新开始这个循环。图 2.15 以 4bit DAC 为例给出了其工作原理示意图,来消除误差。

图 2.15 数字加权平均法循环模型

A. Maloberti 在 1991 年首次提出这种循环选择的方式,这个方法后来被称为数据加权平均法<sup>[35]</sup>。在电路设计过程中,通过一个数字寄存器来储存地址指针PTR,以标识反馈的电容的起始位置 N。若在某周期采用了 V(K)个电容,那么在周期结束时,便将 PTR(K)更新为 PTR(K+1)=PTR(K)+V(K)。[34]中同样给出了对于这种方式中的噪声分析:

$$y_{mis}(k) = IM(ptr(k)) - IM(ptr(k-1))$$

(2.25)

对上式进行 z 变换分析, 可得:

$$Y_{mis}(Z) = (1 - z^{-1}) \cdot IM(PTR(Z))$$

(2.26)

式中 IM(i)为从第 0 到第 i 个器件的失配误差之和。由式(2.26)可知, DWA 方式使得失配噪声经过了一阶整形。结合上一小节已知,由器件失配带来的误差在随机选择情况下会引入白噪声。综上,可以认为通过 DWA 方式能将失配引入的谐波相关噪声打散为白噪声并进行一阶噪声整形。

和 $\Delta\Sigma$  ADC 中的高阶设计思路一致,既然 DWA 算法可以实现一阶噪声整形, 也可以通过不同的算法设计,实现更高阶的失配噪声整形<sup>[38][39]</sup>。但是高阶噪声整 形会使得电路复杂度升高,并且在实际情况下,一阶噪声整形对于大部分的  $\Delta\Sigma$ ADC 而言已经足够。因此,目前采用较多的失配噪声整形方案仍旧是一阶 DWA。

# 2.6 本章小结

本章首先对  $\Delta\Sigma$  ADC 的基础概念和工作原理进行了简单介绍,包括量化噪声、过采样以及噪声整形,并以典型的二阶  $\Delta\Sigma$  ADC 为例,进行了相关信号分析并给出了简单的 MATLAB 仿真结果。其次,介绍了在高阶设计思路受阻时转而采用的多级设计思路,即 MASH ADC。本章在系统层面上对 MASH ADC 进行信号分析的基础上,指出了 MASH 结构的不足以及新的研究方向: SMASH ADC 与Zoom ADC。最后对  $\Delta\Sigma$  ADC 中的积分器和 DAC 两个重要环节进行了介绍,分析了积分器的传递函数,总结了不同积分器结构的优缺点,并对 DAC 中的非理想因素及动态原件匹配方法进行了说明。

# 3 系统架构和理论分析

前两章内容对 ADC 的主要技术指标以及近年来的学术界、产业界成果进行了研究和总结,着重对 MASH ADC 的相关技术基础进行了介绍。本章将在理论分析的基础上,提出系统架构及相关的设计指标,并通过系统层面的仿真结果给出对于模块电路的具体指标要求。

# 3.1 系统设计指标

参数 取值 工作电压(Supply Voltage, VDD) 1.2V 前仿/测试功耗(Power Consumption)  $2.5\mu W/5\mu W$ 带宽(BW) 1kHz 过采样率(OSR) 125 信号-量化噪声比(SQNR) 107dB 信号-噪声失真比(SNDR) 92dB 动态范围(DR) 95dB

表 3.1 2-0 MASH ADC 设计指标

表 3.1 为本文提出的低功耗 2-0 MASHADC 设计指标。围绕低功耗的设计目标,结合学术界调研成果与相关前期仿真,将系统功耗限制在  $5\mu$ W 以内。电源电压采用 55nm CMOS 工艺标准电压 1.2V,估算由寄生电容导致的后仿及测试功耗升高约为前仿的 2 倍,因此要求前仿中功耗指标定为  $2.5\mu$ W。考虑到具体应用场景中传感器需要处理的是变化缓慢但幅值较大的信号,对带宽的要求可以降低,但动态范围要求较高,在此带宽定为 1kHz, DR 定为 95dB。实际测试中,峰值 SNDR 往往略低于 DR,取 15bit 有效位数,则要求  $SNDR = 6.02 \times 15 + 1.76 <math>\approx 92dB$ 。在  $\Delta\Sigma$  ADC 中,由于过采样技术和噪声整形技术,可以较为"廉价"地提高 SQNR,而系统的热噪声则受限于采样电容大小,更大的采样电容意味着更小的噪声和更大的芯片面积,所以对于 SQNR 通常取值为较 SNDR 高 15dB 左

右,定为107dB。在上述指标中,对于有效位数和带宽要求都比较低,但对于功耗的要求较为严苛,因此,在电路设计中需要格外关注功耗要求。

# 3.2 系统架构设计

常见的  $\Delta\Sigma$  ADC 多为二阶或三阶架构,这是考虑到高阶架构中积分器和量化器更容易面临饱和的问题,从而会限制最大可处理输入信号。结合论文高动态范围的设计初衷,在此采用二阶架构。虽然多 bit 量化器能够提供更高的精度并减小环路饱和压力,但会导致较高的功耗,故在此采用单 bit 量化器即比较器以节约功耗。对于最传统的二阶前馈型  $\Delta\Sigma$  ADC Silva—Steensgaard 结构,如图 2.6 所示,在不考虑积分器及量化器饱和情况下的 MATLAB 代码仿真中,OSR=125 时,SQNR 仿真结果仅为 87.25dB,这远低于设计指标,虽然采用更高的 OSR 可以使得精度进一步提高,但这要求更高的工作频率,同样违背了低功耗的设计初衷。所以,本文选择 MASH 架构。

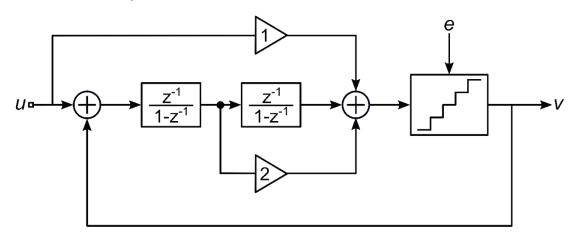

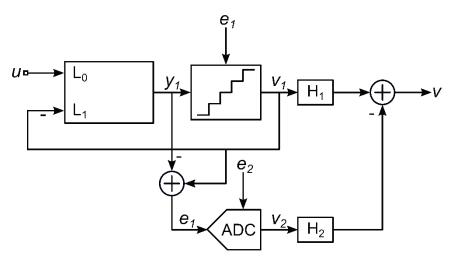

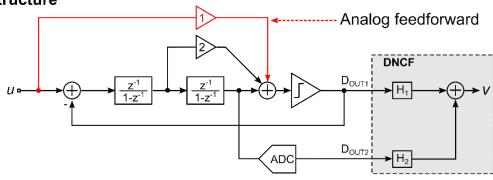

图 3.1 给出了传统 MASH 架构与本文提出的 MASH 架构的对比。在传统架构中,由 2.2.2 节可知,在低扰动前馈型  $\Delta\Sigma$  ADC 结构中,第一级 ADC 中的第二级积分器的输出为量化误差  $e_I$  的延时信号,可以直接用作第二级 ADC 的输入。同时,因为输入信号直接前馈至量化器前端,所以环路中积分器仅需处理误差信号,这使得系统能够处理更大幅值的输入信号,从而提高 SNDR 峰值。

本文提出的架构中,第二级 ADC 采用低精度 SAR ADC 结构实现以节约功耗。若进一步提高噪声整形阶数则需要增加运放,这会带来额外的功耗开销;另一方面,最终的精度可以通过 SAR ADC 的 bit 数进行相应的调节,将在 3.2.1 中给出相关的仿真结果。

在此基础上,本文创新地将前馈通路实现方式由模拟域变为数字域,通过对SAR ADC 的时分复用,在不添加额外电路开销的同时,将输入信号的量化结果直接前馈至比较器的输出端。此时,第一级积分器变为 Zoom ADC,反馈 DAC则变成了多 bit,通过这种方式可以有效地减小第一级环路滤波器中积分器的输出摆幅从而降低了功耗。考虑到 SAR ADC 的位数越多,环路中积分器的输出摆幅越小,但更高位数的 SAR 不仅本身会带来更高的功耗,同时也会使 DAC 所采用 DWA 的功耗也会随位数呈现出指数上升趋势,所以 SAR 的位数不宜太高。

另外,对于 MASH 结构来说,数字前馈通路引入量化噪声的位置与比较器引入量化噪声的位置相同,因此,它们可以一起通过数字噪声消除滤波器(Digital Noise Cancellation Filter, DNCF)在数字域中消除,使得最终的量化结果v中仅有第二级的量化误差,也就是 SAR 的量化误差。由此,输出信号的计算结果为:

$$v = (z^{-2})D_{OUT1} + (1 - z^{-1})D_{OUT2}$$

(3.1)

# Prior structure

(a)传统的模拟前馈型 MASH ADC

(b)论文提出的数字前馈型 MASH ADC 图 3.1 ADC 结构框图

#### 3.2.1 系统参数确定

本文提出的数字前馈型 2-0 MASH ADC 结构中, SAR ADC 的位数需要在精度及功耗两方面之间折衷考量。

提出的 MASHADC 中第一级 ADC 工作方式为 Zoom 结构,通过使反馈电压更加逼近输入信号的方式来减小积分器输出信号摆幅。为了避免 SAR 的量化误差导致的  $V_{REF}$ -与  $V_{REF}$ -区间无法覆盖输入信号,需要增加扩界系数  $M^{[5][6]}$ 。 M=0时无扩界效果,若 M 取太大则会牺牲 SAR 的量化精度。本文取 M=1,输入信号

与反馈信号波形如图 3.2 所示,可以看到即使 SAR 量化结果末位出错,也能够使输入信号处于[ $V_{REF}$ , $V_{REF}$ ]区间内。

图 3.2 扩界系数与参考电压关系

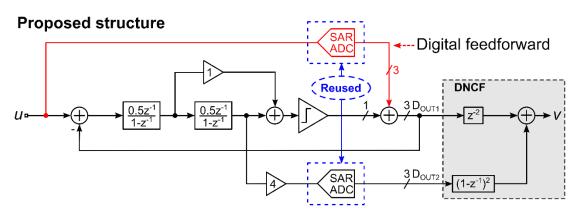

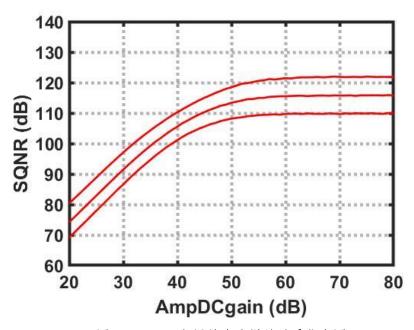

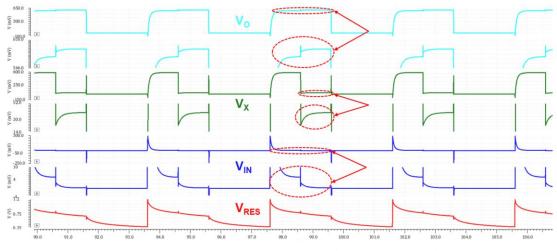

由 2.3 节已知,在 MASH 结构中,运放的增益十分重要,若运放的增益不足,则会导致噪声泄露现象从而降低最终的精度。为了确定该结构对于运放直流增益的要求,对不同增益、不同位数的 SAR ADC 进行了多次 MATLAB 仿真扫描,最终结果如图 3.3 所示。在仿真过程中,1)考虑 SAR ADC 上下限对扩界系数影响,即在 SAR ADC 输出最大值与最小值时无法扩界;2)不考虑积分器与量化器在电路实现中的摆幅影响;3)积分器系数取 0.5,对此将在后文中进行分析;4)两级积分器中运放增益设为相等;5)输入信号幅值取-1.9dBFS,过采样率 OSR=125,每个数据点采用 2<sup>22</sup> 点数进行频谱分析。

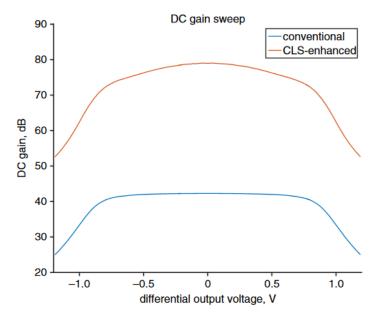

图 3.3 SQNR 与运放直流增益关系仿真图

图 3.3 中从下到上三条曲线分别为 SAR ADC 为 3、4、5 bit 时的仿真结果。可以看出,在运放直流增益较低时,随着运放增益的提高,SQNR 有着明显的提升;当运放增益提高到一定值后,SQNR 基本保持不变。由仿真结果可知,结合设计指标和设计冗余,运放直流增益应为 60dB 以上。

此外,对比三条曲线的仿真结果可知,SARADC 每提高一位,最终 SQNR 增加约 6dB,这与预期一致,因为在经过 DNCF 后,最终的量化误差仅由 SARADC 产生。从仿真结果可知,在 SARADC 取 3bit 时,SQNR 已经达到约 110dB。对于设计目标来说已经足够,所以本文选用 SARADC 的量化位数为 3bit。

但值得注意的是,在选用 3bit SAR ADC 情况下, $\Delta\Sigma$  环路在处理较大幅值输入信号时,仍旧会出现饱和现象。为了进一步降低积分器输出信号摆幅,将两级积分器系数均取为 0.5,前馈系数也相应地做出调整。对于  $\Delta\Sigma$  环路而言,需要在量化器前补充一个 4 倍增益环节以弥补积分器系数,但由于采用比较器作为量化器,其只关心输入信号的正负,而不关心大小,所以可以省略该增益环节。对于 SAR ADC 而言,则需要补充一个 4 倍增益环节,其具体实现方式在后文给出。当 OSR=125 时,该 MASH ADC 结构的采样频率归一化典型 SQNR 仿真结果如图 3.4 所示。

图 3.4 系统典型 FFT 输出频谱(2<sup>16</sup>点)

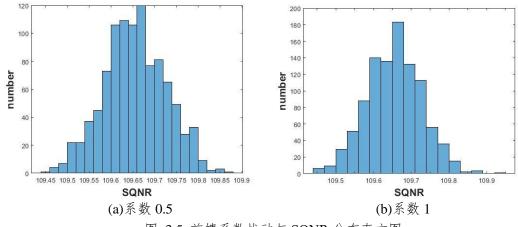

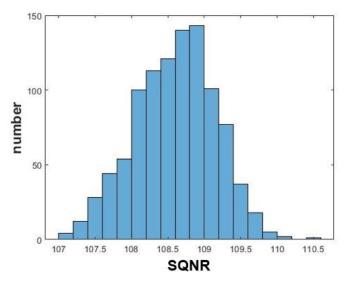

考虑到在芯片在设计及实际制作过程中,可能会受到版图不对称或失配等影响,分别在 MATLAB 代码仿真中增加 normrnd(0, 0.01)的扰动至前馈系数 0.5 与 1,以此模拟非理想因素的影响。1000 个 2<sup>22</sup>点 FFT 分析随机仿真结果直方图如图 3.5 所示,可以看出这些扰动对于系统的量化误差影响较小,可以忽略不计。

图 3.5 前馈系数扰动与 SQNR 分布直方图

由 2.4.2 可知,对于 DT ΔΣ ADC 而言,电路热噪声主要取决于采样电容大小。同时,对于二阶 ΔΣ ADC,第二级热噪声在等效至第一级输入端时,需要除以第一级增益,所以系统热噪声主要受限于第一级采样电容大小,第二级采样电容取值要求则相对较低。本设计中,电容大小取值如表 3.2 所示,具体电路将在 3.3 节给出,其中第二级采样电容取值为第一级电容的 1/4。假设输入正弦信号幅值为 960mV,温度为 300K,采样相位与积分相位噪声贡献相同,可得信号-热噪声比为:

$$SNR = 10 \cdot log \frac{(0.96/\sqrt{2})^2}{4 \cdot (KT/C_{S1})/OSR_{125}} = 94.86dB$$

(3.2)

可以知道理想 SNR 较 SQNR 低约 15dB, 较指标高约 3dB, 满足设计要求并留有一定裕量。

表 3.2 2-0 MASH ADC 电容取值

| 电容                | 设计取值     |

|-------------------|----------|

| C <sub>S1</sub>   | 8×110fF  |

| C <sub>INT1</sub> | 16×110fF |

| $C_{S2}$          | 2×110fF  |

| C <sub>INT2</sub> | 4×110fF  |

| $C_{SAR}$         | 9.5fF    |

| C <sub>F1</sub>   | 52fF     |

| C <sub>F2</sub>   | 52fF     |

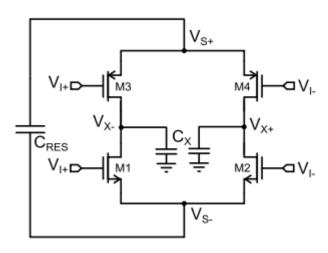

#### 3.2.2 系统电路架构

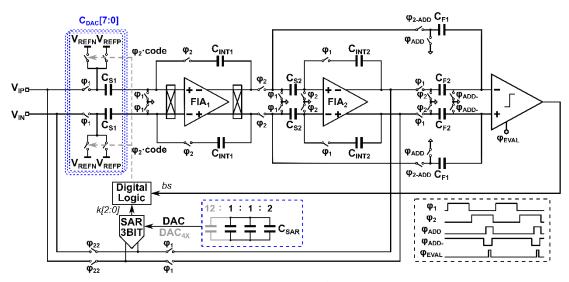

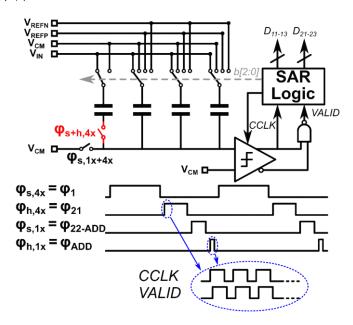

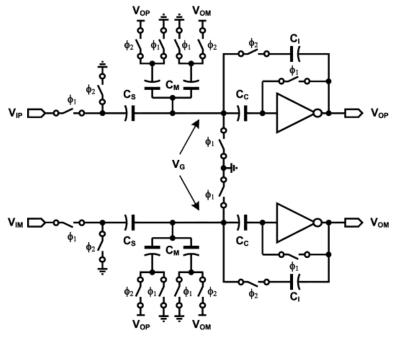

简化的系统电路图与时序图如图 3.6 所示。系统中的异步 3bit SAR ADC 在前馈通路与系统第二级 ADC 之间复用。在作为第二级 ADC 时,四倍量化增益由并联的 12 倍单位电容实现。在第一级积分器前后采用斩波开关以消除 1/f 噪声。

图 3.62-0 MASH ADC 电路结构图

# 3.3 系统关键技术

在系统层面的电路设计主要需要考虑热噪声的大小,1/f 噪声的处理,反馈的 实现方式,系统的时序等问题。其中热噪声大小与电容取值在 3.2.1 系统参数确 定小节已经进行过相关计算。本节主要对其余几个系统关键技术展开分析和讨论。

### 3.3.1 CHOPPER 开关

除了前述的量化噪声与热噪声之外,还需要考虑闪烁噪声对电路的影响。 MOS 管中的闪烁噪声主要来自于单晶硅边界"悬挂"键对载流子的随机捕获和 释放<sup>[40]</sup>。闪烁噪声比热噪声的平均功率更难预测,它受工艺影响很大,可以用一 个与栅极串联的电压源进行模拟,近似的表达式为:

$$\overline{v_n^2} = \frac{\kappa}{c_{OX}WL} \frac{1}{f} \tag{3.3}$$

式中, K 是与工艺有关的常量。通过表达式可知, 其噪声谱密度与频率成反比,

频率越低,噪声密度越大,所以闪烁噪声也叫 1/f 噪声。若要减小 1/f 噪声,就必须增加器件面积。

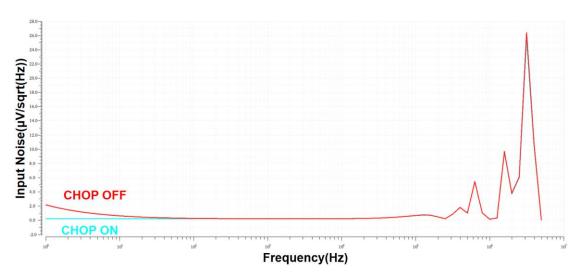

而在 ΔΣ ADC 中,可以采用在第一级积分器前后增加斩波开关的方式将将低频噪声转移至斩波频率附近,同时不影响信号的传输。采用斩波前后的低频噪声功率谱密度差距如图 3.7 所示,可以看到在低频处的 1/f 噪声在斩波之后有了明显的降低。

图 3.7 斩波开关与 1/f 噪声频谱分析

#### 3.3.2 CDAC 复用

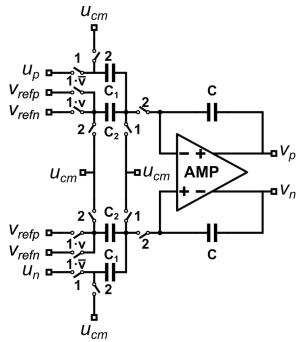

在 DT ΔΣ ADC 中,有两种方式可以实现 CDAC 反馈,分别如图 3.8 和图 3.9 所示。二者的区别在于图 3.8 中的采样电容与反馈电容互相独立,采样电容仅负责转移在采样相位采集到的电荷,在积分相位其输入端与共模电压相连。反馈电容的工作时序与采样电容相同,区别是其采样了 Vrefp 或 Vrefn 的电压。而在图 3.9 中,采样电容与反馈电容为同一个电容,反馈的实现取决于其在积分相位采样电容的输入端所接反馈电压。

由于图 3.9 中少了一组采样电容,所以其噪声相较于图 3.8 降低一半,SNR 可以提高 3dB。但它要求输入电压满幅幅值与参考电压满幅幅值相同,并且容易 出现共模电压失配的影响。考虑到在本设计中输入电压与参考电压满幅幅值相同,故采用图 3.9 所示结构,可以在节约面积的同时获得更高的 SNR。

图 3.8 采样/反馈电容独立型反馈结构

图 3.9 采样/反馈电容复用型反馈结构

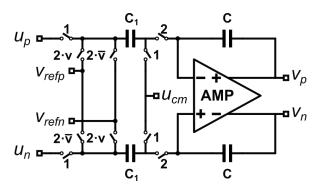

#### 3.3.3 SAR 量化器及复用

在本设计中,3bit SAR ADC 分别被用于数字前馈环节与第二级 ADC,其单 边电路结构示意图与工作时序如图 3.10 所示。在前馈环节中,其工作模式相当于在 Zoom ADC 中量化输入信号,要求其能够迅速完成,故采用异步工作模式。 在理想情况下,希望对输入信号的量化在  $\varphi_1$  开始的瞬间完成,但在本结构中这是无法实现的。因为在  $\varphi_1$  相位中,第二级积分器在进行积分工作,而 SAR ADC 的电容在进行采样已被占用。所以前馈环节的采样与转换环节提前至  $\varphi_{22}$  相位完成;作为第二级积分器工作时在  $\varphi_1$  相位,也就是第二级 ADC 的积分相位进行采样,在  $\varphi_{21}$  相位完成转换。一方面,由于输入信号频率较低,在一个周期内可以视为近似不变,所以由前馈环节量化提前所带来的误差较小;另一方面,该误差

可以被视为量化误差的一部分,同时考虑到扩界系数,所以该误差的影响可以忽略不计。

设计中 3bit 量化精度通过 1:1:2 的采样电容实现,四倍的量化增益通过额外并联 12 倍的单位采样电容实现。在进行四倍增益量化时,将该电容接入电路参与电荷重分配环节,在进行单位增益量化时,断开该电容与比较器输入端的开关将其从电路中分离。

图 3.10 SAR ADC 电路结构与时序图

# 3.4 本章小结

本章针对本论文设计的应用场景提出了相关设计指标,并结合上一章基础知识与当前架构融合的发展趋势,提出了创新的系统架构。接着根据指标的要求对其余系统参数,例如运放增益、SAR ADC 位数、采样电容大小等进行了仿真与估算,为具体的模块电路设计提出了详细要求。最后对系统层面的关键技术进行了研究和分析,通过斩波开关消除 1/f 噪声的影响;通过 CDAC 复用实现了节约芯片面积并降低了采样噪声;通过时分复用 SAR ADC,降低了电路的硬件开销。

# 4 系统模块电路设计

上一章对系统架构和指标及相关关键技术进行了介绍,本章将重点介绍系统中各电路模块的设计思路与工作原理,并进行了相关的仿真分析。模块电路可以分为模拟和数字两部分:模拟电路设计部分包括放大器设计、SAR 量化器设计及升压开关设计;数字电路设计部分包括 DEM 模块与时钟模块。系统在 TSMC 55nm CMOS 工艺下完成了电路设计与仿真验证工作。

# 4.1 放大器设计

在 DT ΔΣ ADC 中,最重要的环节便是其中的积分器,而积分器设计则是以 开关电容电路为基础,其核心还是放大器的设计。这使得高性能的运算放大器设 计成为实现该 ADC 的关键之一。

### 4.1.1 基于反相器的运算放大器设计

随着工艺的进步,近年来的数字芯片设计发展迅速。对于数字电路设计者来讲,他们可以在更小的面积中集成更多的电路,同时随着电源电压的降低,功耗有了明显的下降。与此相对,模拟电路设计则并未显著享受到工艺进步带来的性能提升,其中有许多方面的因素,例如电源电压的降低使得部分电路结构无法适用。在这种发展趋势下,模拟设计者们在 ADC 的设计中开始关注基于反相器的运放设计。Y. Chae 在 2009 年对基于反相器的运放设计进行了详细地研究[41]。

与模拟电路设计中最常见的五管运放相比,反相器结构更为简单,它多由 1 个 PMOS 管和 1 个 NMOS 管构成,且从 VDD 到 GND 之间仅为两"层"MOS 管,比五管运放结构的三"层"还要简化。因此,基于反相器的运放更适合在低电源电压和低功耗的场景下工作。

对于反相器而言,其静态工作点受工艺影响较大,为了使其能够作为运放工作,必须保证 PMOS 管和 NMOS 管均工作在饱和区。设计者可以根据 PMOS 管和 NMOS 管尺寸比例设置合适的输入电压。但在实际制作过程中,由于工艺误差的影响,例如阈值电压 Vth 变化或 MOS 管尺寸变化,会使得这个电压偏离原

先的电压,从而使反相器失去放大功能。

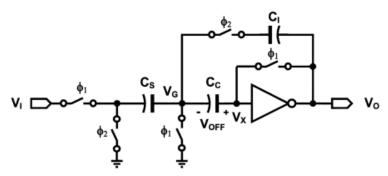

为了解决工艺误差的影响,可以在开关电容电路中的采样相位进行自调零 (Auto Zero, AZ),即在反相器与输入源之间增加隔离电容  $C_{\rm C}$ ,同时在采样相位将反相器输入输出短接,此时,PMOS 管和 NMOS 管均为二极管接法,若电源电压足够,则栅极电压必定为能使两个 MOS 管工作在饱和区的电压。由于反相器的栅极与实际信号输入端隔离,压差会存在  $C_{\rm C}$  电容上,在积分相位仍旧能保持该压差来维持反相器稳定工作。采用反相器运放的开关电容电路如图 4.1 所示。

图 4.1 采用反相器运放的开关电容电路图

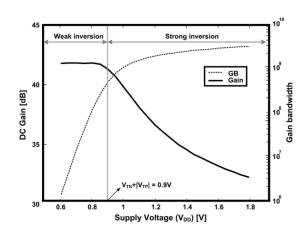

在反相器作为运算放大器工作时,其受电源电压影响较大。如图 4.2 所示,在自调零工作过程中,当电源电压较低时,若 VDD 小于两个 MOS 管阈值电压之和,MOS 管便会进入亚阈值区,跨导 gm 与输出阻抗 Rout 均会升高,可以获得较高的增益;当电源电压较高时,MOS 管则进入饱和区,速度提高但增益相对降低。为了在增益与速度间折衷,一个较为合理的方案是将电源电压设置为两MOS 管 Vth 之和的附近。图 4.2 中,0.9V 就是一个较为推荐的电源电压,兼顾了增益与带宽的需求,此时增益约为 40dB。

图 4.2 反相器运放直流增益/增益带宽积与供电电压关系图

由于反相器本质上相当于单输入单输出运放, 若在全差分结构中将其用于处

理相位相反的正负两信号,则形成伪差分结构,如图 4.3 所示,此时共模反馈 (Common mode feedback, CMFB) 电路是必需的。

图 4.3 反相器运放的开关电容电路共模反馈电路图

### 4.1.2 电平偏移增益提高技术

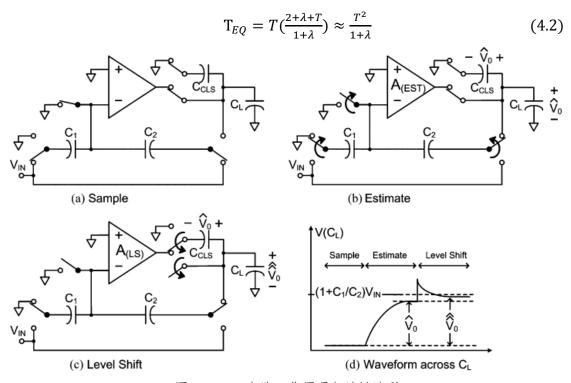

如前文的图 4.2 所示,单级反相器所能提供的最大增益约为 40dB,这往往是不够的。为了提高增益,有许多方法,但都有其所对应的缺点,例如通过级联的方式提高增益的 RingAmp<sup>[42]</sup>,需要考虑建立时间并且可能会引入稳定性的问题;还可以通过 cascode 方式提高输出阻抗从而提高增益<sup>[26]</sup>,但这种方式会减小运放的输出摆幅(output swing),这与低电源电压电路设计的大前提相悖。

除此之外,在开关电容电路中,还可以通过相关电平偏移(CLS)增益提高技术 实现更高的增益。它本质上是单级运放,不会带来稳定性的问题,也不会损失输 出摆幅,但作为代价的是其需要相对复杂的相位控制以及额外的电容 Ccts<sup>[43]</sup>。

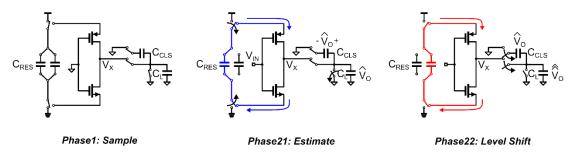

CLS 的具体工作方式如图 4.4 所示。在采样相位,CLS 电容 C<sub>CLS</sub> 与负载电容 C<sub>L</sub> 并联,一同作为负载电容。积分相位被分为两个相位,分别是粗放大相位 Estimate 与二次放大相位 Level Shift,其中在粗放大相位与普通的电荷放大器的电荷转移过程并无区别;在二次放大过程中,C<sub>CLS</sub> 的下级板与共模电压 V<sub>CM</sub> 断开,同时运放的直接输出与输出节点断开并与 C<sub>CLS</sub> 的下级板相连。由于电容两端电压不能突变,C<sub>CLS</sub> 在粗放大相位存储了输出电压 Vo,此时运放的直接输出

节点会重新变回 V<sub>CM</sub>,而输入端仍旧有残余电压,所以运放会进入二次放大过程。 通过理论计算可知, CLS 技术会使得运放的等效增益变为原先的平方倍,可 表示为:

$$\widehat{\widehat{V_O}} = V_{IN} \left( 1 + \frac{c_1}{c_2} \right) \left( \frac{T}{T+1} \right) \left( \frac{2+\lambda+T}{1+\lambda+T} \right) \tag{4.1}$$

式中,T 为环路增益, $\lambda$  为表示有限  $C_{CLS}$  影响的一个系数,它由各电容取值和运放原本增益决定。考虑有限增益对开关电容闭环放大精度的影响,可得等效环路增益  $T_{EO}$ :

图 4.4 CLS 电路工作原理与关键波形

在 2017 年,H. Zhang 结合了基于反相器的运算放大器与 CLS 技术,实现了单级高增益反相器运放,其电路结构和简化时序如图 4.5 所示,仿真结果如图 4.6 所示 $^{[44]}$ 。图中, $\phi_1$ 、 $\phi_{21}$ 、 $\phi_{22}$ 分别对应 Sample、Estimate、Level Shift 相位。需要注意的是,在 CLS 技术应用中,需要在 Estimate 相位使得 C<sub>CLS</sub> 电容上采样到输出电压的变化值,对于反相器而言,输出电压在 Estimate 相位开始时为 AZ 结束时的输出电压,为了能够准确地创造出该电压,需要另一个同样尺寸的反相器进行驱动。但这种方法会导致较大的功耗。一个可行的替代方案为采用沟道长度 L 较大的 MOS 管构成的反相器进行驱动,此时两管阻值较大,可以有效减小功耗,但这可能会由于器件匹配不好造成  $V_{CLS}$  电压不准确从而降低增益。文中则是巧

妙地利用了另一级积分器中的反相器运放提供驱动,若第一级积分器在积分相位,则第二级积分器在采样相位,即运放处在 AZ 状态,并不会导致额外的功耗。

图 4.6 的仿真结果显示通过 CLS 技术,将运放的峰值增益从 42dB 提升至 79dB。同时,还将运放的有效输出摆幅从 55%提升至 80%。

图 4.5 采用 CLS 技术的反相器运放电路与时序图

图 4.6 采用 CLS 技术的反相器运放直流增益与输入幅值关系图

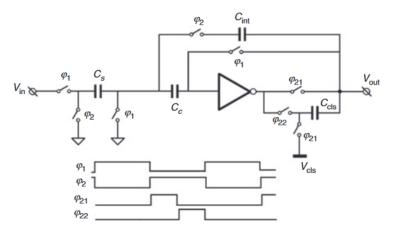

2019 年, X. Tang 提出了 FIA。这是一种动态放大器,适用于开关电容电路中,可以进一步降低功耗,并且具有不需要 AZ 工作以及共模反馈电路和 PVT 稳定的优点,其电路结构如图 4.7 所示[12][13]。

图 4.7 浮动反相放大器(FIA)电路图

与传统的运算放大器相比,FIA 最为突出的特点便是将供电由电压源转换为电容 Cres 供电。在采样相位,Cres 充电至 VDD,反相器与供电电容断开,不消耗功耗;在积分相位,Cres 与反相器相连,提供驱动能力,反相器可以进行放大,在整个放大过程中,Cres 的电压不断降低,一旦降低为 PMOS 与 NMOS 阈值电压之和,该电路自然关断。通过调整其容值,可以使得其在电荷转移完成后及时关断,从而最大限度地降低功耗。

而与传统的基于反相器的运放相比,FIA 最为突出的特点是不需要 AZ 相位。在采样相位,其输入输出均连接至  $V_{CM}$  电压,在积分相位运放工作时,环路中电流流向如图 4.8 所示。AZ 的本质为在供电电压区间内,找到合适的输入电压值,使得 PMOS 与 NMOS 同时工作在饱和区,区别在于 AZ 操作是通过改变输入电压幅值实现,而 FIA 则是通过改变供电电压区间实现。例如,若输入电压幅值偏高,则会导致 N 管导电能力强,P 管导电能力弱, $V_{S}$ -迅速上升,同时,由于电容两端电压不能突变,会导致  $V_{S+}$ 上升,作为结果,会导致 N 管导电能力减弱,P 管导电能力增强。工艺角对于该电路的影响可以转换为输入共模电压的影响,例如 FS 工艺角的情况可以类比为输入共模电压偏高。

由于电流环路中在理想情况下不存在其它电流通路,所以无论 Ix,cm 流出多少,仍旧会有同样多的电流流入,所以理想情况下该电路输出共模电压稳定,不需要 CMFB。但在实际电路中,由于在 CRES 两端存在寄生电容的影响,CRES 放电时 IAMP-需要对两寄生电容 CP 充电,所以共模电压会存在一些变化。共模电压的变化值由式(4.3)给出

$$\Delta V_{X,CM} \approx -2 \cdot V_{I,CM} \cdot \frac{c_P}{c_X} \tag{4.3}$$

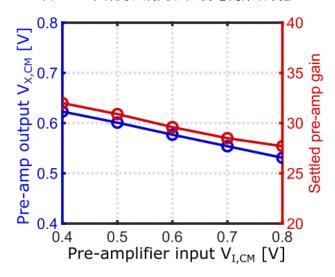

可以看出 $\Delta V_{CM}$ 与 $C_P$ 大小成正比,与 $C_X$ 大小成反比。由于 $C_P$ 难以控制,这就要求FIA 采用较大的负载电容,此时会导致较大的功耗。运放输出共模电压与增益随输入共模电压的变化如图 4.9 所示。在 2021 年,X. Tang 发表的论文 $^{[15]}$ 中 所采用的三级FIA 采用了简单的CMFB 以进一步稳定输出电压共模值。

图 4.8 浮动反相放大器共模电流分析模型

图 4.9 浮动反相放大器输出共模电压/增益与输入共模电压关系仿真结果

#### 4.1.3 结合电平偏移增益提高技术的浮动反相放大器

从基于反相器的运放近几年研究趋势来看,一些在原先静态工作时可以采用的技术,在动态结构中也可以尝试。例如静态工作中的多级反相器运放 RingAmp结构<sup>[42]</sup>,在动态结构中可以变为多级 FIA 级联<sup>[14][15]</sup>;通过 cascode 方式增大输出电阻的方式也可以在 FIA 中采用;通过在反相器 AZ 相位时利用电流源分别设置 PMOS 与 NMOS 栅压来增加输出电压摆幅<sup>[45][46]</sup>,在动态结构中可以变为摆幅增强型浮动反相放大器(Swing Enhanced FIA, SEFIA)<sup>[47]</sup>。由此,本文将 CLS 技术应用于 FIA,提出了新的运放结构。

考虑到单级放大器所能提供增益有限,约为40dB。而由3.2.1节已知,为了使得MASH结构具有较高SQNR,需要设计运放具有60dB以上直流增益。所以还需要对FIA进行改进。若采用级联的方式会带来稳定性的问题,文献[14][15]通过调整C<sub>RES</sub>电容大小关系使得FIA从导通到关断时的极点变化趋势不同,从而实现环路稳定,但采用级联方式会引入较大的C<sub>RES</sub>,需要占用更多的芯片面积。cascode方式则是以运放的输出摆幅为代价获得增益的提高<sup>[15]</sup>,然而在低电源电压设计方时,这种方式则变得不那么实用。

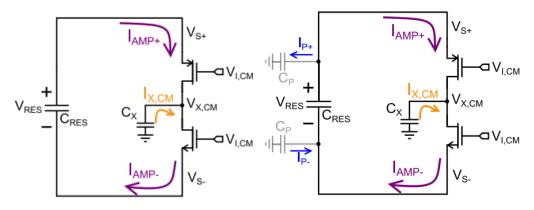

考虑到系统对运放的实际要求,并结合近年来学术界研究成果,本文首先提出了"FIA+CLS"的创新组合以实现单级高增益运算放大器,其简化的单边结构与工作时序如图 4.10 所示。在三个相位它们工作流程如下:

- Sample 相位:供电电容 C<sub>RES</sub> 分为两部分,在该相位对 C<sub>RES</sub> 充电,同时运放停止工作以节约功耗,将运放的输入输出节点电压重置为 V<sub>CM</sub>;

- Estimate 相位:采用其中一个 C<sub>RES</sub> 供电,进行粗放大工作。在这个过程中 C<sub>L</sub> 与 C<sub>CLS</sub> 同时作为负载电容,大量的电荷转移工作在这个相位已经完成;

- Level Shift 相位: 将 C<sub>CLS</sub> 下极板与 V<sub>CM</sub> 断开, 反相器直接输出节点 V<sub>X</sub> 与输出节点 V<sub>0</sub> 断开, 并使二者相连, 并将另一个 C<sub>RES</sub> 电容接入电路提供驱动能力,由于该相位为增益提高过程,仅需要转移少量的电荷,所以该相位的 C<sub>RES</sub> 可以取较小容值以降低功耗。

提出的"FIA+CLS"组合同时还具有另外两个优势:

1.由于输出共模电压稳定,且运放在每个放大相位开始时,输出电压均从  $V_{CM}$  开始变化,这使得  $C_{CLS}$  的下级板在采用  $V_{CM}$  时能够准确记录输出电压变化幅度,从而在 Level Shift 相位开始时  $V_X$  节点可以重新回到  $V_{CM}$ 。由于不需要额外提供  $V_{CLS}$  电压,该结构可以进一步降低功耗;

2.由于 FIA 工作时输出电压摆幅的稳定依赖于  $C_{RES}$  两端寄生电容与负载电容的的比值  $C_P/C_X$ 。 $C_P$  在取定运放参数后便基本确定,仅能通过版图优化来尽可能减小。在 Estimate 相位时, $C_{CLS}$  与  $C_L$  同时作为负载电容,这使得  $C_X$  取值较原先增大,从而提供了更稳定输出共模电压。

图 4.10 结合 FIA 与 CLS 技术的电路工作时序

### 4.1.4 动态体偏置

在"FIA+CLS"组合中,可以发现它采用了两个供电电容  $C_{RES}$ 。为了进一步对电路进行简化,提高能效,本设计在此基础上提出了动态体偏置方案,其简化的单边结构与工作时序如图 4.11 所示。较 4.1.3 中方案减少了一个  $C_{RES}$ ,增加了两个选择开关。在三个相位它们工作流程如下:

- Sample 相位:运放重置方式同前一小节。由于运放已经停止工作,所以其体 电位不影响运放工作特性,本设计中在该相位将其源衬短接。

- Estimate 相位: 运放粗放大工作方式同前一小节。在该相位中,分别将 PMOS体电位与 VDD 相连,将 NMOS体电位与 GND 相连。随着 C<sub>RES</sub>的放电,PMOS与 NMOS的源端电压分别呈现出降低与上升趋势,由于体效应,会使得二者阈值电压之和 Vth,sum=|Vthp|+|Vthn|呈现出上升趋势,从而使得运放提前关断。

- Level Shift 相位: 运放二次大工作方式同前一小节。区别之处在于在该相位中,运放额外的驱动能力并不需要一个新的 C<sub>RES</sub> 电容提供,仅需要将两 MOS 管更改为源衬短接的形式,由仿真可知,两管阈值电压之和会减小约 100mV。由于大部分电荷转移过程在上一相位已完成,所以这微小的阈值电压变化足以使得运放完成二次放大工作。该结构中额外的 Level Shift 相位功耗仅来源于 C<sub>RES</sub> 电容的进一步放电。

图 4.11 动态体偏置辅助的 FIA+CLS 电路工作时序

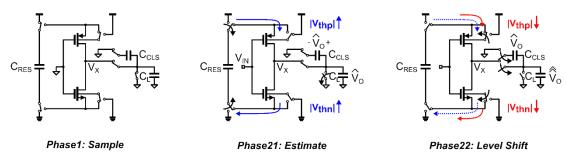

提出的运放电路仿真结果如图 4.12 所示,包括  $V_O$ 、 $V_X$ 、 $V_IN$  的电压波形及局部放大图与  $V_{RES}$  的电压波形。可以看到输出电压  $V_O$  在切换至 Level Shift 相位后进行了二次放大过程,其电压较上一相位的稳定电压有了再次抬升;运放的直接输出电压  $V_X$ 则是在 Level Shift 相位开始瞬间降低至  $V_{CM}$ ,随后进行了二次放大过程;运放的输入端  $V_{IN}$  由于二次放大,使得残余电荷被进一步转移,运放的虚地特性更加理想,从而使运放体现出了更高的直流增益; $V_{RES}$  电压在整个放大过程经历了二次放电,可以明显看出在 Level Shift 相位放电远低于 Estimate 相位,这与预期一致。

图 4.12 动态体偏置辅助的 FIA+CLS 电路关键波形仿真图

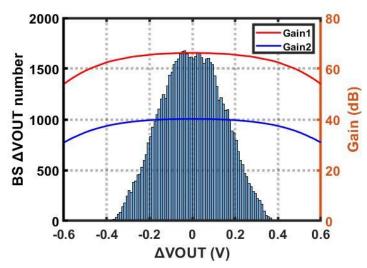

运放增益随输出电压变化趋势以及系统在理想情况下第一级积分器的输出分布结果如图 4.13 所示,图中 Gain1 为经过 CLS 技术之后的运放直流增益,Gain2 为未采用 CLS 技术时的运放直流增益。可以看到在采用 CLS 技术之后,增益峰值由 Gain2 的 40.2dB 提升为 Gain1 的 66.2dB。仿真条件中,运放相关参数与第一级积分器相同,采样电容为 8×110fF,积分电容为 16×110fF,负载电容为 2×110fF+52fF;系统工作周期取了 2<sup>16</sup> 周期,输入信号幅值为-1.9dBFS。可以看到,第一级积分器的输出电压幅值基本处于-0.4V 至+0.4V 之间,在该区间内,

运放的增益曲线较为平缓,在±0.4V时,增益仅下降了0.8dB,可以认为该运放设计能够保证系统正常工作;在250kHz时钟频率工作时,运放的平均功耗仅为308nA。

图 4.13 系统第一级积分器输出信号分布直方图及运放直流增益与输出信号幅值关系

### 4.2 SAR 量化器

如前所述,在系统的前馈支路与第二级输出结果的量化过程采用了一个 3bit SAR 量化器,其复用时序在 3.3.3 已经进行了相关说明。本节主要对该量化器的三个主要构成部分进行分析说明,分别是动态比较器、SAR 逻辑与 DAC。

#### 4.2.1 动态比较器

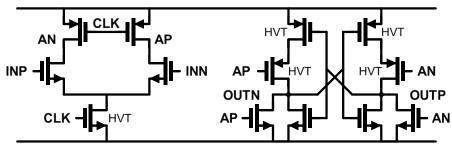

考虑到低功耗的设计要求,SAR量化器设计采用的是动态比较器。该动态比较器分为预放大级与锁存器两部分构成,如图 4.14 所示。在时钟信号到来之前,电路处于关断状态,此时预放大级输出节点 AN/AP 被充电至 VDD,两比较器输出均被重置为 GND。通过采用高阈值电压 MOS 管(High Vth MOSFET, HVT MOS)可以有效降低关断状态下的电路的漏电功耗<sup>[48]</sup>。在时钟信号上升为高时,预放大级电路导通,根据输入信号幅值关系,AN与 AP会以不同斜率下降,该趋势会被第二级锁存器捕捉并锁存,最终输出比较信号 OUTP与 OUTN。

在该电路设计中,需要进行折衷考量的主要集中在预防大级。由于动态比较器的功耗来源于节点的充放电,所以 MOS 管尺寸越小,比较器的功耗越低。但

输入对管的尺寸太小会加剧器件失配(mismatch)带来的影响,同时输入对管宽长 比的取值也对比较器的速度会产生一定的影响。

图 4.14 动态比较器电路图

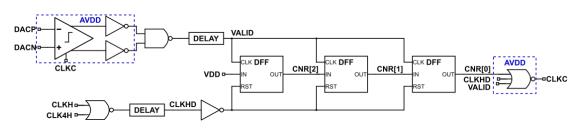

#### 4.2.2 SAR 逻辑

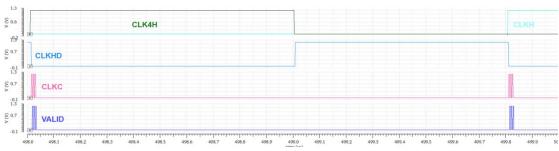

在论文的电路设计中,为了与工作时序相匹配,SARADC采用了异步逻辑,因此可以在一个周期中很短的时间内完成量化,简化的控制逻辑如图 4.15 所示。CLKH 与 CLK4H 分别为单位增益量化与四倍增益量化转换开始信号,由其它模块提供。当这两个信号均为低电平时,CLKHD 为高电平,CLKC 始终为低,SAR停止工作;其中之一变化为高电平时,转换可以进行。CNR[n]为级联 D 触发器的输出信号,该输出信号由 VALID 驱动,每当比较器比较完成一次,便会有一位由低跳高,CNR[0]表示所有转换均已完成。在 CLKHD 与 CNR[0]均为低时,表示转换已开始,但未完成,逻辑控制环路由比较器驱动信号 CLKC 与比较完成信号 VALID 组成,在比较器比较工作完成时,两输出不同,经过 DELAY 模块后 VALID 升高,从而使 CLKC 降低,比较器重置,由图 4.15 知,在比较器重置时两输出均为低,经过 DELAY 后,VALID 降低,使得 CLKC 升高,开始下一个比较周期。关键逻辑信号仿真结果如图 4.16 所示。

图 4.15 SAR ADC 控制逻辑电路图

图 4.16 SAR ADC 控制逻辑电路关键波形仿真图

### 4.2.3 量化器仿真结果

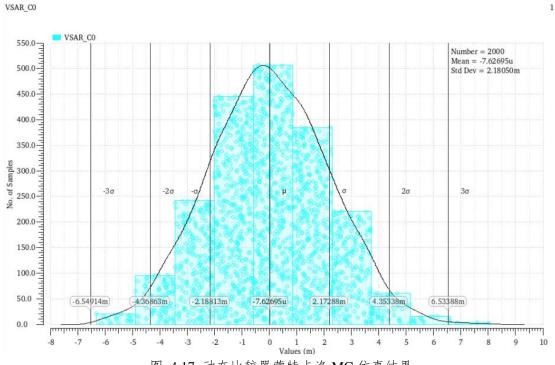

SAR ADC 中的动态比较器的蒙特卡洛(Monte Carlo, MC)仿真结果如图 4.17 所示, 仿真条件为仅比较器采用实际电路器件, 为了得到较为准确的仿真结果, 采用了 10bit SAR ADC, 参考电压差分值定为 20mV, 在输入短接情况下进行 MC 仿真。由 2000 点仿真结果可知, 失配会给 SAR ADC 造成平均值约+11.9043 μV, 方差 2.18mV 的偏差。

图 4.17 动态比较器蒙特卡洛 MC 仿真结果

单独对比较器进行噪声仿真,可得其噪声水平约为 $\sigma=0.35$ mV,在此基础上,对 SAR ADC 中的采样电容添加 normrnd(0,0.01)的非理想扰动,即 1%的失配影响,并代入图 4.17 中的比较器蒙特卡洛仿真结果,重新进行 MATLAB 仿真。1000 个系统  $2^{16}$  点信噪比仿真结果如图 4.18 所示。SAR ADC 中这些非理想因素对系统影响较小,可以忽略不计。

图 4.18 SAR ADC 非理想因素影响的系统 SQNR 分布直方图

# 4.3 升压开关

在高精度  $DT\Delta\Sigma$  ADC,对于采样开关也需要格外重视,若采样信号不能准确反映输入信号,则会使建立误差(settling error)增大,无论后续环节如何准确,系统最终的信噪比也无法提升。

通常情况下, MOS 管在作为开关使用时工作在线性区以实现更小的开关电阻, 所以传输高电平时采用 PMOS, 传输低电平时采用 NMOS, 而传输变化幅度较大的信号或中间电平时, 则采用 NMOS 与 PMOS 互补的传输门即可。

对于输入信号而言,采用传输门仍旧难以满足要求,在这种情况下有两种升压开关采用 NMOS 作为开关管的方案可以考虑。其中一种是将 NMOS 栅压控制信号升至 2×VDD,这种方案的好处在于实现较为简单,同时由于栅压较高,使得开关管电阻足够小,基本可以忽略阻抗变化的影响。缺点在于可能会由于栅压过高造成开关管击穿,因此需要器件具有较高的耐压才可使用。

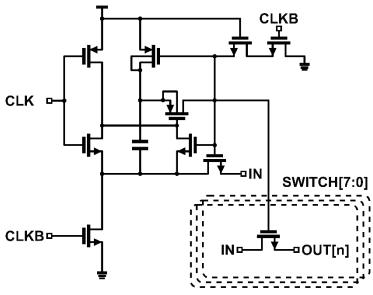

另一种方案是本设计中采用的 bootstrap 采样开关,如图 4.19 所示。这种方案中,栅压始终比输入信号高一个 VDD 电压,从而维持在器件允许的耐压范围内,并且保证了开关电阻不随输入信号变化,抑制了谐波。考虑到本设计中为多bit CDAC 反馈方式,bootstrap 电路需要一个相对较大的电容,因此,在时序允许的情况下,采用一个升压后的控制信号同时控制多个开关管以节约版图面积。

图 4.19 bootstrap 采样开关电路图

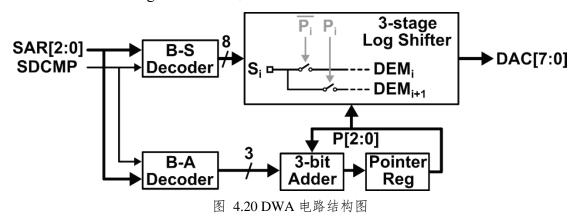

# 4.4 DEM 模块

在低功耗设计前提下,由于一阶失配噪声整形对于目前的系统而言已经足够,所以本设计中采用最简单的 DWA 实现方式,如图 4.20 所示。由于反馈信号实际上是由 3bit SAR ADC 量化结果与 1bit 比较器量化结果共同决定,所以是在 2<sup>4</sup>=16 种组合中实现将反馈电压划分为 8 个区间共 9 种状态的反馈电压组合。因此首先需要一个 4 输入 8 输出的译码器,决定反馈电压;此外还需要一个 4 输入 3 输出的译码器和累加器及指针配合,实现累加计数与偏移;反馈电容的循环方式则是通过指针和 3 阶 Log Shifter 电路实现。

# 4.5 时钟模块

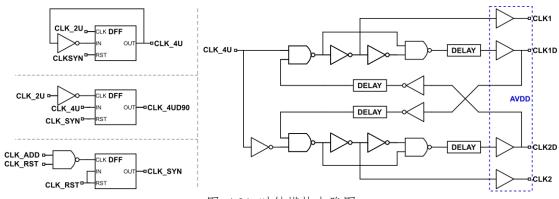

系统采样频率为 250kHz, 考虑到 CLS 技术需要将积分相位分为 Estimate 与

Level Shift 两个部分,所以芯片实际输入时钟采用 500kHz。主要时钟模块如图 4.21 所示。对输入时钟进行二分频之后得到周期 T = 4μs 的时钟信号 CLK\_4U。 采用该信号经过传统的非交叠时钟产生电路生成 CLK1/CLK1D/CLK2/CLK2D 四个时钟信号。对输入时钟进行反向并对 CLK\_4U 进行采样,可以获得相位相差 90°的 CLK\_4UD90 信号。具有 90°相位差的两个 T=4μs 的时钟可以与后续时钟进行逻辑运算,得到 CLS 工作需要的 CLK11/CLK12/CLK21/CLK22 信号。

图 4.21 时钟模块电路图

在电压域分配上,所有数字逻辑均采用 DVDD 与 DGND,采用的 NMOS 为

无深 N 并结构,其体电位即为 P 型衬底。所有的模拟管均采用 AVDD 与 AGND,采用的 NMOS 为有深 N 并结构,其体电位与 P 型衬底隔离。考虑到 CLK1 等时钟信号直接控制采样开关,而采样开关与模拟信号相连,所以时钟信号的缓冲器供电采用 AVDD 与 AGND。

# 4.6 本章小结

本章介绍了 2-0 MASH ADC 中主要电路模块的工作原理和设计。对于本文提出的采用动态体偏置并结合 CLS 技术的 FIA,详细讨论了其设计思路与工作原理,并给出了仿真结果;对 SAR 量化器中的各个小模块进行了说明,并在电路仿真提取参数之后回代 MATLAB 仿真,验证了非理想因素对系统的影响;除此之外,还介绍了升压开关、DEM 模块与时钟模块。仿真结果表明,各模块电路功能均符合设计指标要求,且留有裕量,足以支持系统正常工作。

# 5 版图设计与仿真及测试结果

上一章对系统的各个模块电路的工作原理进行了介绍,并给出了相关仿真结果。本章将从系统层面上进行仿真验证,分别给出 ADC 整体的前仿与后仿频谱分析,并对版图布局进行介绍。最后对实际的流片测试结果进行总结与分析。

# 5.1 系统功能验证

在 3.2 节中给出了系统架构并确定了系统参数,同时给出了 MATLAB 代码层面的 ADC 理想仿真结果。但代码层面的仿真还是过于理想化,没有考虑增益非线性等诸多因素。在第四章已经给出符合设计预期的各个模块电路仿真结果,本章将结合设计的电路进行整个 ADC 的系统功能验证,系统电路如图 3.6 所示。

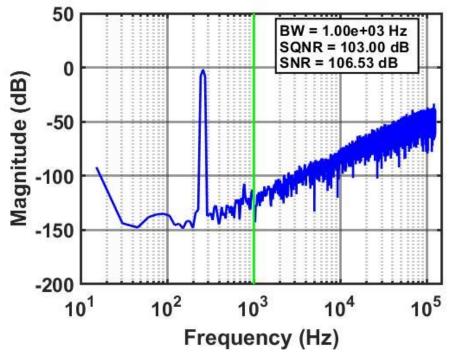

### 5.1.1 量化噪声仿真结果

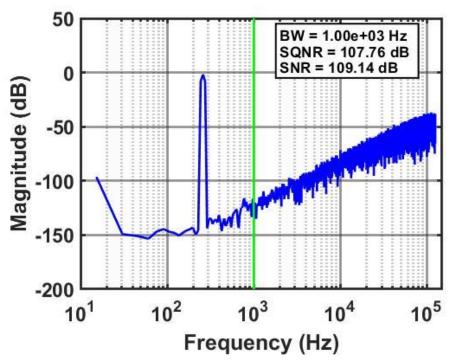

系统 SQNR 仿真结果如图 5.1 所示。仿真条件为全部采用实际的晶体管级器件,考虑芯片 IO 影响,给出实际上电时序,输入信号幅值为-1.9dBFS。由于仿真耗时较长的原因,仿真结果仅为 2<sup>14</sup>点 FFT 频谱。在此仿真点数较少,但已经足够观察结果。尽管更多的点数可以使得带内噪底进一步降低,但即使点数进一步升高,实际仿真得到的信噪比并不会有太大变化。

图 5.1 系统电路 SQNR 前仿典型 FFT 输出频谱(2<sup>14</sup>点)

从图中可以看出,在 1KHz 带宽内,可以实现 SQNR = 107.76dB。虽然与MATLAB代码仿真得到的110dB有所偏差,但仍旧能够满足107dB的设计指标。对于这部分偏差可能有两方面原因:

- 1.误差导致的偏差。由于仿真点数不够多,在仿真中会出现±2dB 范围内的 波动,最大可以达到 3dB,因此,该仿真结果处于合理的误差范围内;

- 2. 非线性的影响。在实际电路中存在许多非线性影响,例如采样开关电阻值的变化,虽然通过升压开关保证 V<sub>GS</sub> 恒定,但受到体效应影响,其 Vth 仍然会随输入信号变化,从而导致电阻变化;运放在不同输出幅值输出信号时直流增益不同,可能会引起谐波,从图中可以看出三次谐波略高于噪底。

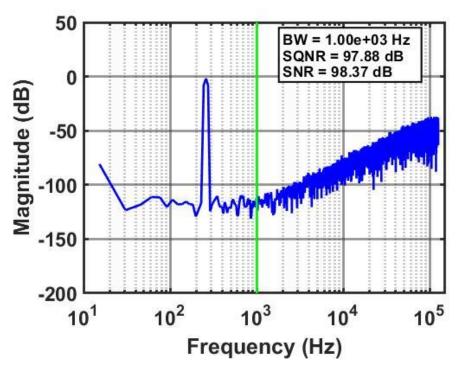

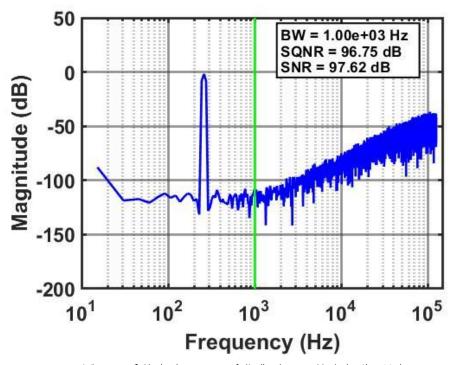

#### 5.1.2 系统整体仿真

系统 SNDR 的仿真结果如图 5.2 所示。仿真条件为 SQNR 仿真基础上,添加瞬态噪声 Tnoise, Tnoise 频率设置范围取 1Hz 到 20×fs = 5MHz。

图 5.2 系统电路 SNDR 前仿典型 FFT 输出频谱(214点)

对比上一小节 SQNR 仿真结果,可以发现 FFT 频谱中,二者趋势相同。由于系统受限于热噪声,所以频带内由热噪声主导,呈现出白噪声特性,无法看到噪声整形效果。最终能够得到 SNDR = 97.88dB,这与式(3.2)计算有一定偏差,该仿真结果较理论计算结果高约 3dB,有两方面的原因:

一方面是因为式(3.2)仅为较为粗略的估算,实际上在采样相位与积分相位的 热噪声贡献不能简单视作相同,一个更详细的计算方式应为<sup>[20]</sup>:

$$\overline{v_n^2} = (\frac{kT}{C_{S1}})(2 + \frac{\gamma_{amp} - 1}{1 + x})$$

(5.1)

式中, $\gamma_{amp}$ 为代表运放噪声贡献的一个参数,在最好的情况下, $\gamma_{amp}=2/3$ ,x 为运放增益  $x=g_m*R$ 。然而,即使是该式也是基于一系列假设与近似得出的结论,并且其适用于普通的运放,对于本文的动态运放而言,由于运放的带宽和增益会随时间变化,情况会更为复杂,所以理论计算值仅能作为参考。

另一方面是仿真设置带来的问题。在采样相位对采样开关和采样电容组成的RC 网络进行积分得到了 kT/C 的结论,然而由于 RC 的值较小,所以带宽较大,为 GHz 级别,在仿真中 Tnoise 上限频率则仅为 5MHz,缺少了从该上限频率到RC 截止频率之间的噪声,所以仿真结果中基本没有采样相位的热噪声影响,而积分相位运放参与工作,带宽会受限于运放,此时 Tnoise 上限频率足够覆盖实

际噪声带宽。所以, 仿真结果中热噪声会缺少采样相位的部分, 导致其噪声约为理论值的 1/2, 使得仿真 SNDR 比理论计算约高 3dB。

由于仿真速度与噪声频率上限相关。虽然可以在仿真时将噪声频率上限调高到 GHz 级别,但仿真时长会大大加长,这是设计周期所不能允许的。因此,仿真工作中维持 Tnoise 上限为 5MHz 的设置,预期实际测试结果会较仿真结果低约 3dB 即可。此外,在多次电路修改过程中,可以发现 SNDR 波动约为±1dB。在这个区间内都认为仿真结果正常。

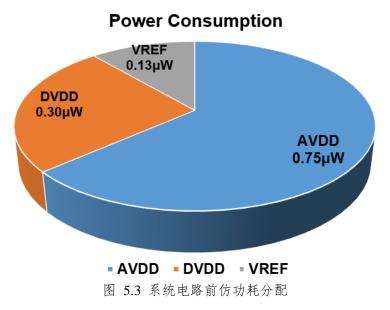

#### 5.1.3 功耗分配

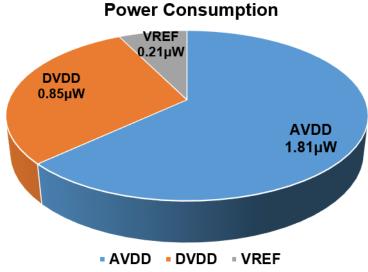

前仿的功耗分配如图 5.3 所示,总功耗为  $1.18\mu W$ 。可以看出模拟电路部分占据了较大的功耗,数字电路部分其次,参考源消耗的功耗最少。这是一个相对合理的功耗分配方式,对于  $\Delta\Sigma$  ADC 而言,AVDD 与 VREF 供电电路主要包括积分器与比较器等"能够提供分辨率"的模块,而 DVDD 供电电路则主要包括时钟电路、DWA 电路等不可缺少、但"不提供分辨率"的模块。例如,如果在目前的电路基础上,仅将采样电容与积分电容等比例增大,则 DVDD 占比会进一步缩小,受限于热噪声的 SNDR 将会提高。但考虑到低功耗设计目标,所以在此不予以考虑。

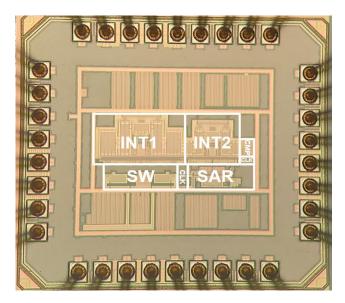

# 5.2 版图设计和后仿验证

本设计在 TSMC 55nm CMOS 工艺完成版图绘制,由于以研究为主,所以引脚数目较多,共34 引脚,芯片总面积受限于引脚数目,为0.797mm²,实际核心电路占用面积较小,仅为0.136mm²。芯片面积占用并不突出,原因为其中含有Trim 电容等冗余部分,且 FIA 依靠电容供电,所以电容面积较大。

#### 5.2.1 版图设计

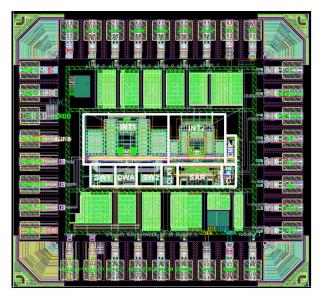

最终版图设计如图 5.4 所示(省略 dum 图层)。整体布局思路为模拟区域与数字区域分离,信号流向为从左至右,可以看到上半部分为模拟区,包括两级积分器与比较器,下半部分则为数字模拟混合区域,考虑到 DWA 连线较多,若走线过长会由于寄生参数引起较大功耗,所以将走线路径减短作为前提,将 DWA 模块置于 bootstrap 模块 SW1/SW2 之间。其中 CLK1 模块负责产生全局使用的时钟信号,所以将其置于中心位置。SAR ADC 需要采样输入信号与第二级输出信号,将其置于第二级积分器正下方,其中 SAR DAC 在该模块左方,SAR Logic 在该模块右方,左方与 CLK1 维持了一定间距。CLK2 负责提供与前馈信号控制及SAR Logic 局部采用的时钟信号,所以将其布局在右下角。

整体布局思路为首先保证模拟区域与数字区域隔离,而在数字区域则在模拟数字区域隔离的基础上还需综合考虑模块间互连线长短的问题。除了芯片核心区域与必要的 IO 及 ESD 电路之外,为了满足工艺手册的要求、获得更稳定的电源电压以及出于设计规则验证(Design Rule Check, DRC)的密度要求,在芯片中其余部分填充了去耦电容。

图 5.4 芯片版图设计

芯片照片如图 5.5 所示。在照片中仅能看到顶层金属相关信息。

图 5.5 芯片照片

芯片共采用 34 个引脚,其分配与功能介绍如表 5.1 所示。 表 5.1 芯片引脚分配

| Γ             | 水 3.1 ベカオMMの TEL                             |  |  |  |  |

|---------------|----------------------------------------------|--|--|--|--|

| 引脚名称          | 作用                                           |  |  |  |  |

| AVDD/AGND     | 芯片内模拟模块供电电源, 1.2V 供电/模拟地。                    |  |  |  |  |

| DVDD/DGND     | 芯片内数字模块供电电源, 1.2V 供电/数字地。                    |  |  |  |  |

| VREFP/VREFN   | ADC 参考电压供电电源, 1.2V 供电/信号地。                   |  |  |  |  |

| VDD/VSS(2)    | IO 端口芯片内侧引脚, 1.2V 供电, 提供输出驱动与静电保护。           |  |  |  |  |

| VDDPST/GNDPST | IO 端口芯片外侧引脚, 2.5V 供电, 提供输出驱动与静电保护。           |  |  |  |  |

| POC           | 上电控制信号(Power on control),与 VDDPST 在 PCB 级短接。 |  |  |  |  |

| VINP/VINN     | 平衡模式输入信号。                                    |  |  |  |  |

| VCM           | 共模电压输入引脚。                                    |  |  |  |  |

| CLK_2U_IN     | 500kHz 时钟输入引脚。                               |  |  |  |  |

| CLK_ADD_IN    | SAR ADC 时分复用控制时钟输入引脚。                        |  |  |  |  |

| CLK_RST       | 重启信号,也用于产生同步时钟信号。                            |  |  |  |  |

| CHOP_ON       | 斩波开关控制信号。                                    |  |  |  |  |

| DWA_ON        | 动态原件匹配模块控制信号。                                |  |  |  |  |

| A1TD[2:0]     | 第一级积分器 Trim 引脚, 用于调节 C <sub>RES</sub> 电容大小。  |  |  |  |  |

| A2TD[2:0]     | 第二级积分器 Trim 引脚,用于调节 C <sub>RES</sub> 电容大小。   |  |  |  |  |

| DOUT1[2:0]    | SAR ADC 对输入信号的量化结果。                          |  |  |  |  |

| DOUT2[2:0]    | SAR ADC 对第二级积分器输出信号的量化结果。                    |  |  |  |  |

| DOUT3         | ΔΣ ADC 量化器(比较器)输出结果。                         |  |  |  |  |

| CLK1_OUT      | 系统时钟输出引脚,用于提供采样时钟。                           |  |  |  |  |

| -             |                                              |  |  |  |  |

### 5.2.2 系统后仿指标验证

在完成版图绘制之后,对芯片提取寄生参数并系统进行了后仿验证。此时 SQNR 与 SNDR 仿真结果分别如图 5.6 和图 5.7 所示。仿真条件与前仿条件相同,在后仿提取寄生参数时由于受限于仿真速度和所需时间,所以仅提取 C+CC。

图 5.6 系统电路 SQNR 后仿典型 FFT 输出频谱(214点)

图 5.7 系统电路 SNDR 后仿典型 FFT 输出频谱(214点)

从图中可以看到由于寄生参数影响,在 SQNR 仿真中出现了明显的三次谐波,使得 SQNR 较前仿降低约 5dB。结合中间仿真过程,在单独替换各个模块时并未出现 SQNR 明显下降的情况,推测其原因为模块间互连线导致的积分器负载电

容增大从而限制了运放的增益。但在 SNDR 仿真中可以发现,该三次谐波被热噪声淹没, SNDR 仅较前仿低了约 1dB,仍旧符合设计预期。

芯片后仿的功耗分配如图 5.8 所示。其总功耗为 2.86μW, 较前仿 1.18μW 上升了约 2.4 倍。从其占比变化可以发现 DVDD 供电模块占比上升, 从原先的占比 25%上升至占比 30%。芯片总功耗上升幅度比预期更大, 但仍满足指标要求。

### 5.3 芯片测试

最终芯片的采用 JLCC44 封装。在测试环节可以进行相对大量的数据测试以验证芯片功能。在此对典型 FFT、动态范围、芯片功耗进行了测试,并对多片芯片在电源电压变化情况下进行了稳定性测试。

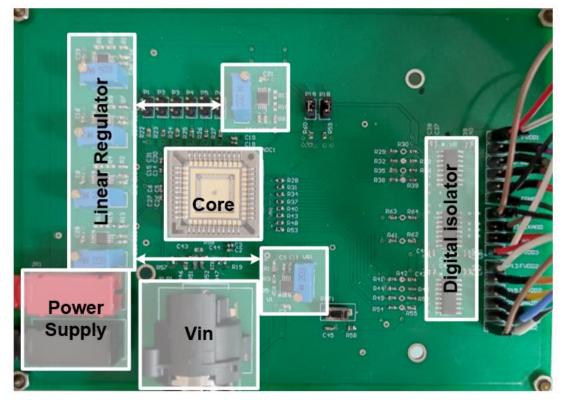

### 5.3.1 测试 PCB

芯片测试 PCB 如图 5.9 所示。其中模拟部分主要布局在 PCB 板的左侧,数字输出部分布局在 PCB 板的右侧。PCB 采用+5V 电源电压供电,为了分别测试不同模块的功耗以及符合标准 IO 要求,芯片有多个供电引脚,由电源电压经过线性稳压器进行供电。输入信号采用平衡线输入。输出数字信号经过数字隔离器件输出至逻辑分析仪进行数据采集。

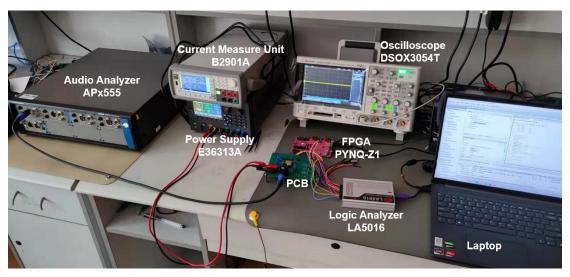

图 5.9 测试 PCB 照片

测试平台照片如图 5.10 所示。测试过程中,供电电源采用 E36313A 提供+5V 电源电压给 PCB; 音频分析仪 APx555 提供高精度正弦信号作为信号输入; 芯片功耗测量采用精密电流表 B2901A; 示波器 DSOX3054T 用于检测关键电压波形; 与计算机相连的 FPGA PYNQ-Z1 与逻辑分析仪 LA5016 分别用于控制输入时钟信号与捕获输出数字信号; 最后输出数据在计算机中进行分析与处理。

图 5.10 测试平台照片

### 5.3.2 系统测试结果

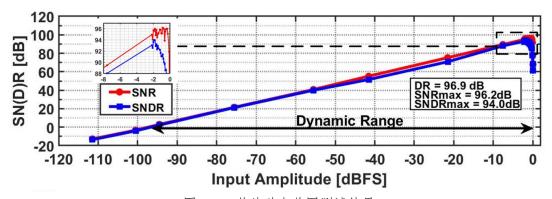

芯片典型输出数据频谱分析结果如图 5.11 所示。测试条件为输入信号幅值为 -1.9dBFS,输入信号频率为 278.5Hz,采用  $2^{16}$ =65536 点数 FFT 分析。最终测得 系统 SNDR = 94.0dB,SNR = 95.8dB,SFDR = 99.8dB,符合设计预期。

与后仿结果相比,可以发现其 SNDR 降低了约 3dB。这与前述的式(3.2)与式(5.1)结果符合的较好。除此之外,后仿时仅提取了 C+CC 指标,没有提取 R 以及 L,后仿仍旧不够精确,所以测试与后仿及理论计算会存在一些误差。

图 5.11 芯片输出频谱测试结果(216点)

芯片测试功耗分配如图 5.12 所示。测得总功耗为 2.87μW,与后仿符合得较好。各供电电源功耗占比也与后仿近似。从功耗分配可以侧面说明芯片工作与预期相符。

图 5.12 芯片功耗分配测试结果

芯片前后仿真与测试的对比结果如表 5.2 所示。

表 5.2 系统关键指标前后仿与测试结果对比

|             | 前仿     | 后仿     | 测试    |  |

|-------------|--------|--------|-------|--|

| SQNR(dB)    | 107.76 | 103.00 | NA    |  |

| SNDR(dB)    | 97.88  | 96.75  | 94.00 |  |

| Power( µ W) | 1.18   | 2.85   | 2.87  |  |

### 5.3.3 动态范围测试

ADC 动态范围测试结果如图 5.13 所示。测试结果表明,本文所提出 ADC 可以达到动态范围为 96.9dB。符合设计指标要求。峰值 SNDR 可以达到 94.0dB,峰值 SNR 可以达到 96.2dB。在低功耗设计前提下仍旧具有较高的精度和动态范围。

图 5.13 芯片动态范围测试结果

#### 5.3.4 电源电压变化影响

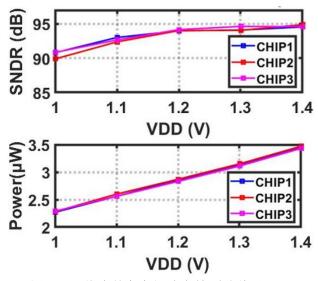

芯片 SNDR/功耗受供电电压影响的测试结果如图 5.14 所示。共对三片芯片进行了测试,电源电压范围在标称 1.2V 基础上波动±0.2V。从测试结果可以看出,在供电电压足够高的情况下,芯片 SNDR 表现稳定;在供电电压降低的情况下,SNDR 呈现出下降趋势。原因为积分器种 FIA 采用 CRES 供电,CRES 所能支持的有效工作范围仅为[[Vth,sum],VDD]区间,随着 VDD 的降低,电容供电能力不足,无法支持完整的电荷转移过程,使得运放增益下降,从而导致最终 SNDR下降。芯片功耗随供电电压升高呈现出升高趋势,这与预期相符。

图 5.14 芯片供电电压稳定性测试结果

## 5.4 本章小结

本章首先通过前仿从 SQNR/SNDR/功耗等方面验证了系统的性能。接着介绍了芯片的版图布局,并给出了对应的后仿结果,针对后仿与前仿的差异提出了可能的原因分析。最后介绍了芯片测试 PCB 的布局,并给出了芯片的 SNDR/功耗/DR/供电电压相关的测试结果,与仿真结果进行了对比,并对测试结果进行了相关分析。

从测试结果来看,本设计较好地完成了设计预期指标。最终测得 FoM<sub>SNDR</sub> = 179.4dB, FoM<sub>DR</sub>=182.3dB。与近年来 10μW 以下各结构 ADC 学术成果对比如表 5.3 所示。本设计在采用全动态电路,较好地实现了低功耗 ADC 设计目标,在相 关工作中具有最高动态范围,且具有较为突出的 FoM 值。

表 5.3 近年来低功耗 ADC 性能对比(<10μW)

|                          | ISSCC-18 <sup>[49]</sup><br>Hariprasad<br>Chandrakumar | ISSCC-19 <sup>[4]</sup><br>Mario<br>Konijnenburg | ISSCC-21 <sup>[50]</sup><br>Kyojin<br>Choo | ISSCC-21 <sup>[51]</sup> Corentin Pochet | ISSCC-21 <sup>[52]</sup><br>Jiannan<br>Huang | This work |

|--------------------------|--------------------------------------------------------|--------------------------------------------------|--------------------------------------------|------------------------------------------|----------------------------------------------|-----------|

| Architecture             | SDCT                                                   | NS-SAR                                           | SAR                                        | VCO                                      | VCO                                          | SDDT      |

| Process[nm]              | 40                                                     | 55                                               | 180                                        | 65                                       | 65                                           | 55        |

| <b>Fully Dynamic</b>     | No                                                     | No                                               | Yes                                        | No                                       | No                                           | Yes       |

| Fs[kHz]                  | 400                                                    | 32                                               | 6                                          | 200                                      | 64                                           | 250       |

| OSR                      | 40                                                     | 107                                              | 1                                          | 100                                      | 64                                           | 125       |

| BW[kHz]                  | 5                                                      | 0.15                                             | 3                                          | 1                                        | 0.5                                          | 1         |

| Supply[V]                | 1.2                                                    | 1.3/0.9                                          | 1                                          | 1.2/0.8                                  | 0.8                                          | 1.2       |

| Power[µW]                | 4.5                                                    | 0.9                                              | 0.468                                      | 5.8                                      | 1.68                                         | 2.87      |

| SNDR[dB]                 | 93.5                                                   | 78.8                                             | 86.9                                       | 92.3                                     | 94.2                                         | 94.0      |

| DR[dB]                   | 96.5                                                   | NA                                               | NA                                         | 92.3                                     | 95.1                                         | 96.9      |

| FoM <sub>SNDR</sub> [dB] | 184.0                                                  | 161.1                                            | 184.9                                      | 174.7                                    | 178.9                                        | 179.4     |

| FoM <sub>DR</sub> [dB]   | 187.0                                                  | NA                                               | NA                                         | 174.7                                    | 179.8                                        | 182.3     |

$FoM_{SNDR} = SNDR + 10log_{10}(BW/Power)$

$FoM_{DR} = DR + 10log_{10}(BW/Power)$

浙江大学硕士学位论文 第六章 总结与展望

# 6 总结与展望

随着 IoT 的发展,智能传感器日益普及,生产生活中对 ADC 的需求量逐渐上升。在这些容易面临电池供电导致电源受限的情况中,要求 ADC 具有较低的功耗;同时,为了保证满足分辨率需求以及适应复杂的应用环境,芯片的信噪比以及 PVT 稳定性要求也越来越高。本文所提出的数字前馈型 2-0 MASH ADC 结构,创新地在 Zoom ADC 的基础上应用了 MASH 结构,并对 SAR ADC 进行了复用;在电路设计层面,创新地结合了 FIA 与 CLS 方式,并提出了动态体偏置技术,使得电路实现了较高的性能。其具体特点如下:

- 1.系统设计方面,采用数字前馈型 MASH 结构。对于第一级 ADC,采用 SAR ADC 作为前馈支路量化器并将其输出结果与比较器输出结果结合,它实际已经转化为 Zoom ADC 工作模式,并且反馈 DAC 变为多 bit。这有利于减小积分器信号摆幅并减小功耗。在此基础上,通过调整两级积分器系数为 0.5,使积分器输出信号摆幅进一步减小,符合电路可实现要求;

- 2.电路模块设计方面,结合调研结果与低功耗运放设计发展趋势,创新地提出了 FIA+CLS 结构。该结构仅为单级运放,无需考虑稳定性问题,它同时具有二者的优点,即不需要共模反馈电路,PVT 稳定,具有较高增益。所付出的代价为更复杂的时序与额外的 CcLs 电容,但 FIA 结构的输出共模电压的稳定依赖于更大的负载电容,CcLs 的引入恰好弥补了这一点;同时,FIA 在采样相位时输出电压重置为 VcM,这也使得 CLS 技术在应用于反相器运放时无需担心 VcLs 驱动的问题。最终实现了高增益、低功耗以及 PVT 稳定的单级运放;

- 3.在整体电路及版图设计方面,通过对 SAR ADC 的时分复用,节约了大量芯片面积。反馈 DAC 与采样电容复用,减小了噪声的同时节约了芯片面积。通过对版图的合理布局,分隔了模拟区域与数字区域,在数字区域进行布线优化,减小了信号线间寄生,从而尽可能地抑制了由寄生电容带来的功耗上升。

本文设计的低功耗 2-0 MASH ADC 在 TSMC 55nm CMOS 工艺下完成了电路与版图设计、并进行了流片测试。设计的 ADC 带宽为 1kHz,测试结果表明系统整体功耗为  $2.87\mu$ W,在 278.5Hz、-1.9dBFS 输入时,达到最高 5NDR = 94.0dB。系统的动态范围可以达到 5DR = 96.9dB。在电源电压变化的情况下,仍旧可以维

浙江大学硕士学位论文 第六章 总结与展望

持相对稳定的工作。最终通过测试数据可以计算得到  $FoM_{SNDR} = 179.4dB$ , $FoM_{DR} = 182.3dB$ 。在近年来的低功耗 ADC 中表现突出。

尽管如此,本设计仍旧存在一些不足和可以改进的地方:

- 1.仿真工作仍旧不够完善。例如在发现后仿 SQNR 较前仿有了较大的降低时,做出推测为积分器负载电容升高导致。此时可以增大 CRES 或调整运放参数再次进行仿真,但受限于流片日程安排,发现 SNDR 仍旧符合设计指标,就没有进行相关修改;

- 2.在 PVT 稳定性测试时,受限于测试条件,仅测量了三颗芯片在不同电源电压下的工作特性。测试数量较少,并不能有效代表不同工艺角下的工作情况,并且没有测试在温度变化时系统的工作特性;

- 3.最终的测试结果虽然功耗与后仿符合的较好,但 SNDR 较后仿下降了约 3dB,仍旧未能准确定位到原因,仅能做出一些合理猜测。

随着物联网技术不断飞速发展,传感器的需求仍旧会不断上升。为了满足日益严苛的客户需求,延长供电受限情况下产品的使用时长,低功耗 ADC 仍旧具有很大的应用空间。在 ADC 架构设计中,近年来不断有新的融合不同架构的 ADC 以取长补短: 在中等精度应用方面,以 SAR ADC 为基础的多种融合架构例如 NS SAR ADC 分辨率逐渐提高; 在高精度应用方面,以  $\Delta\Sigma$  ADC 为基础的例如 Zoom ADC 则取得了越来越低的功耗。在电路设计层面上,越来越多的静态电路相关技术被 FIA 结构所采用,同时,以 FIA 为基础的运放已经应用在 NS SAR ADC、Pipeline ADC、 $\Delta\Sigma$  ADC 多种结构中。相信这种研究趋势仍旧会不断发展下去。在不久的将来,低功耗应用领域中哪种结构的 ADC 能占据主导位置仍未可知。

# 参考文献

[1] B. Murmann, "ADC Performance Survey 1997-2021," [Online]. Available: http://web.stanford.edu/~murmann/adcsurvey.html.

- [2] J. Liu, D. Li, Y. Zhong, et al. A 250kHz-BW 93dB-SNDR 4<sup>th</sup>-Order Noise-Shaping SAR Using Capacitor Stacking and Dynamic Buffering[C] // 2021 IEEE International Solid-State Circuits Conference (ISSCC). IEEE, 2021, 369-371

- [3] T. H. Wang, R. Wu, V. Gupta, et al. A 13.8-ENOB 0.4pF-CIN 3<sup>rd</sup>-Order Noise-Shaping SAR in a Single-Amplifier EF-CIFF Structure with Fully Dynamic Hardware-Reusing kT/C Noise Cancelation[C] // 2021 IEEE International Solid-State Circuits Conference (ISSCC). IEEE, 2021, 374-376

- [4] M. Konijnenburg, R. van Wegberg, S. Song, et al. A 769μW Battery-Powered Single-Chip SoC With BLE for Multi-Modal Vital Sign Health Patches[C] // 2019 IEEE International Solid-State Circuits Conference (ISSCC). IEEE, 2019, 360-362

- [5] S. Karmakar, B. Gònen, F. Sebastiano, et al. A  $280\mu W$  dynamic-zoom ADC with 120dB DR and 118dB SNDR in 1kHz BW[C] // 2018 IEEE International Solid-State Circuits Conference (ISSCC). IEEE, 2018, 238-240

- [6] S. Karmakar, B. Gönen, F. Sebastiano, et al. A 280 μW Dynamic Zoom ADC With 120 dB DR and 118 dB SNDR in 1 kHz BW[J]. IEEE Journal of Solid-State Circuits, 2018, 53(12): 3497-3507

- [7] E. Eland, S. Karmakar, B. Gönen, et al. A  $440\mu W$ , 109.8dB DR, 106.5dB SNDR Discrete-Time Zoom ADC with a 20kHz BW[C] // 2020 IEEE Symposium on VLSI Circuits (VLSIC). IEEE, 2020, 1-2

- [8] T. Hung, J. Wang and T. Kuo, A Calibration-Free 71.7dB SNDR 100MS/s 0.7mW Weighted-Averaging Correlated Level Shifting Pipelined SAR ADC with Speed-Enhancement Scheme[C] // 2020 IEEE International Solid-State Circuits Conference (ISSCC). IEEE, 2020, 256-258

- [9] L. Fang, T. Fu, X. Wen, et al. A 1GS/s 82dB Peak-SFDR 12b Single-Channel Pipe-SAR ADC with Harmonic-Injecting Cross-Coupled-Pair and Fast N-replica Bootstrap

Switch Achieving 7.5fj/conv-step[C] // 2021 IEEE Custom Integrated Circuits Conference (CICC). IEEE, 2021, 1-2

[10]S. Oh, Y. Oh, J. Lee, et al. A 80dB DR 6MHz Bandwidth Pipelined Noise-Shaping SAR ADC with 1–2 MASH structure[C] // 2020 IEEE Custom Integrated Circuits Conference (CICC). IEEE, 2020, 1-4

[11]S. Oh, Y. Oh, J. Lee, et al. An 85 dB DR 4 MHz BW Pipelined Noise-Shaping SAR ADC With 1-2 MASH Structure[J]. IEEE Journal of Solid-State Circuits, 2021, 56(11):3424-3433.

[12]X. Tang, B. Kasap, L. Shen, et al. An Energy-Efficient Comparator with Dynamic Floating Inverter Pre-Amplifier[C] // 2019 Symposium on VLSI Circuits (VLSIC). 2019, 140-141

[13] X. Tang, L. Shen, B. Kasap, et al. An Energy-Efficient Comparator With Dynamic Floating Inverter Amplifier[J]. IEEE Journal of Solid-State Circuits, 2020, 55(4):1011-1022.

[14] X. Tang, X.Yang, J.Liu, et al. A 13.5b-ENOB Second-Order Noise-Shaping SAR with PVT-Robust Closed-Loop Dynamic Amplifier[C] // 2020 IEEE International Solid-State Circuits Conference (ISSCC). IEEE, 2020, 162-164

[15] X. Tang, X. Yang, J. Liu, et al. A 0.4-to-40MS/s 75.7dB-SNDR Fully Dynamic Event-Driven Pipelined ADC with 3-Stage Cascoded Floating Inverter Amplifier[C] // 2021 IEEE International Solid-State Circuits Conference (ISSCC). IEEE, 2021, 376-378

[16] Analog Devices. AD7788\_7789 datasheet.

https://www.analog.com/media/en/technical-documentation/data-

sheets/AD7788\_7789.pdf

[17] Analog Devices. LTC2440 datasheet.

https://www.analog.com/media/en/technical-documentation/data-sheets/2440fe.pdf

[18] Texas Instruments. TLA202x datasheet.

https://www.ti.com.cn/cn/lit/ds/symlink/tla2021.pdf?ts=1636431880503

[19]Maloberti, Franco. 数据转换器[M]. 西安交通大学出版社, 2013.

[20] Shanthi Pavan, Richard Shreier, Gabor Temes. Understanding delta-sigma data

converters[M]. Wiley, 2017

[21] R. M. Gray and D. L. Neuhoff, Quantization. [J]. IEEE Transactions on Information Theory, 1998, 44(6): 2325-2383

- [22] J. Silva, U. Moon, J. Steensgaard, et al. Wideband low-distortion delta-sigma ADC topology[J]. Electronics Letters, 2001, 37(12):737.

- [23] J. Steensgaard-Madsen, High-Performance Data Converters. [J]. Madsen, 1999.

- [24]T. C. Leslie and B. Singh. An improved sigma-delta modulator architecture[C] // IEEE International Symposium on Circuits and Systems (ISCAS). IEEE, 1990, I-372-375

- [25]J. Silva, U. Moon and G. C. Temes. Low-distortion delta-sigma topologies for MASH architectures[C] // 2004 International Symposium on Circuits and Systems (ISCAS). IEEE, 2004, I-1144

- [26] R. Brewer, J. Gorbold, P. Hurrell, et al. A 100dB SNR 2.5MS/s output data rate  $\Delta\Sigma$  ADC[C] // 2005 IEEE International Digest of Technical Papers. Solid-State Circuits Conference (ISSCC), 2005, 172-591

- [27] N. Maghari, S. Kwon and U. Moon. 74dB SNDR multi-loop sturdy-MASH delta-sigma modulator using 35dB opamp gain[C] // 2008 IEEE Custom Integrated Circuits Conference (CICC). IEEE, 2008, 101-104

- [28] C. Han, N. Maghari. Delay based noise cancelling sturdy MASH delta-sigma modulator[J]. Electronics Letters, 2014, 50(5):351-353.

- [29] C. Han, A. Fahmy and N. Maghari. Noise-cancelling sturdy MASH delta-sigma modulator[C] // IEEE International Symposium on Circuits and Systems (ISCAS). IEEE, 2016, 1502-1505

- [30] L. Samid and Y. Manoli. The nonidealities of multibit continuous-time sigma delta modulators [C]. IEEE International Conference on Electronics, Circuits and Systems (ICECS), 2003, 2: 790-793

- [31] J. A. Cherry and W. M. Snelgrove. Loop delay and jitter in continuous-time delta sigma modulators[C] // IEEE International Symposium on Circuits and Systems (ISCAS), 1998, I-596-599.

- [32]S. Azzouni, N. Khitouni and M. S. Bouhlel. Excess loop delay compensation

techniques in continuous-time  $\Delta\Sigma$  modulators[C]. International Conference on Advanced Systems and Emergent Technologies (IC ASET), 2019, 279-283.

- [33]L. R. Carley. A noise-shaping coder topology for 15+ bit converters[J]. IEEE Journal of Solid-State Circuits, 1989, 24(2): 267-273.

- [34]O. J. A. P. Nys and R. K. Henderson. Analysis of dynamic element matching techniques in sigma-delta modulation[C] // IEEE International Symposium on Circuits and Systems (ISCAS), 1996, I-231-234.

- [35]R. T. Baird and T. S. Fiez. Improved  $\Delta\Sigma$  DAC linearity using data weighted averaging[C] // IEEE International Symposium on Circuits and Systems (ISCAS), 1995, I-13-16.

- [36] C. D. Thompson and S. R. Bernadas. A digitally-corrected 20b delta-sigma modulator [C] // Proceedings of IEEE International Solid-State Circuits Conference (ISSCC). IEEE, 1994, 194-195

- [37] M. Sarhang-Nejad and G. C. Temes. A high-resolution multibit Sigma Delta ADC with digital correction and relaxed amplifier requirements[J]. IEEE Journal of Solid-State Circuits, 1993, 28(6): 648-660.

- [38] R. K. Henderson and O. J. A. P. Nys. Dynamic element matching techniques with arbitrary noise shaping function[C] // IEEE International Symposium on Circuits and Systems (ISCAS). IEEE, 1996, I-293-296

- [39] J. Hu, J. A. Hegt, A. H. M. van Roermund, et al. Higher-Order DWA in Bandpass Delta-Sigma Modulators and its Implementation[C] // IEEE International Symposium on Circuits and Systems (ISCAS), 2016, 73-76.